# NOVEL DIGITAL SYSTEMS DESIGNS FOR SPACE PHYSICS INSTRUMENTATION

### **GEORGE DEKOULIS, BEng (Hons)**

Submitted for the Degree of Doctor of Philosophy to Lancaster University Department of Communication Systems

June 2007

### **Abstract**

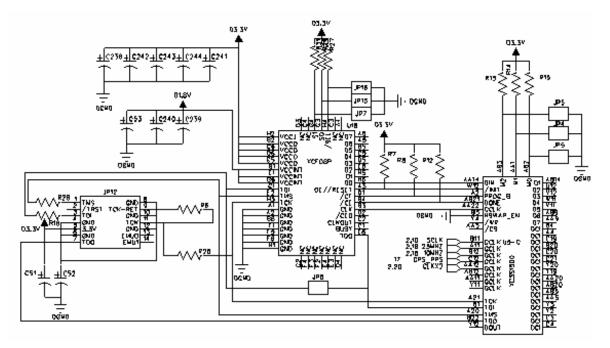

This thesis presents the development of two novel Space Plasma Physics instruments. The few costly space weather missions (SOHO, CHAMP etc.) are justified on the qualitative basis of technological capabilities, such as high-resolution magnetometry, UV, X-ray and stray light imaging power etc. Space weather can also be studied from ground. The demands for ground measurements have increased significantly over the recent years (e.g. THEMIS field-of-view is enhanced by ground instruments). Costs associated with cleanroom procedures, space qualification, launch and operation are avoided. Low-cost ground instrumentations are easier to maintain and upgrade. Controlled high-resolution experiments demand the development of low-noise, interference immune, multi-frequency, multi-bandwidth, multi-dynamic range and multi-integration time instrumentations. Frequency ranges outside the bands of spaceborne instruments are demanded, increasing the range of scientific observations. In-situ data timestamping, real-time clock support and geographical position are demanded for synchronisation with other networked data sets. Performing experiments using different parametric sets or autonomous event-triggered observations demand programmable and dynamically reconfigurable instrumentations.

This thesis initially presents the design of a custom dual-channel cross-correlator data acquisition system. The cross-correlator is later incorporated into the two novel riometer (PRIAMOS) and magnetometer (DIMAGORAS) systems. The primary goal of Priamos is the upper-atmospheric absorption measurement of the highly energetic galactic electrons emissions superimposed on the Cosmic Microwave Background and other last scattering surface galactic and extragalactic radio astronomical background emissions. Priamos surveys accurate right ascension positions with an unprecedented combination of frequency, bandwidth and sensitivity, compared to existing widebeam riometers, providing in-depth observations of the different Space Physics events. It is the first riometer equipped with a programmable saturation protection circuit, enabling measurements of strong Solar Radio Emissions. Dimagoras measures the Earth's field disturbed magnetic flux density due to Space Physics events. The results of a novel applied design methodology for engineering low-power macroscale optimised sensors, also suitable for aerospace applications, are presented, which yielded to the development of a tri-axial fluxgate sensor. Space Physics events are measured in detail due to the receiver's programmable dynamic range, resolution and integration time.

i

## **Contents**

| Abstract                                                    | i   |

|-------------------------------------------------------------|-----|

| Acknowledgements                                            | xii |

| 1. Introduction                                             | 1   |

| 2. Background Theory                                        |     |

| 2.1 Background                                              | 7   |

| 2.2 Riometry                                                | 11  |

| 2.2.1 Widebeam Riometers                                    | 11  |

| 2.2.2 Imaging Riometers                                     | 14  |

| 2.2.3 Solar Wind-Magnetospheric-Ionospheric Riometer Events | 16  |

| 2.2.3.1 Cosmic Noise Absorption (CNA)                       | 18  |

| 2.2.3.2 Auroral Absorption                                  | 19  |

| 2.2.3.3 Polar Cap Absorption (PCA)                          | 19  |

| 2.2.3.4 Sudden Ionospheric Disturbances (SIDs)              | 20  |

| 2.2.3.5 Ionospheric Scintillation                           | 22  |

| 2.2.3.6 Solar Radio Emissions (SREs)                        | 22  |

| 2.2.3.7 Lightning                                           | 24  |

| 2.2.3.8 Interference                                        | 24  |

| 2.3 Magnetometry                                            | 26  |

| 2.3.1 The Earth's Magnetic Field                            | 26  |

| 2.3.2 Sensors Comparative Analysis                          | 27  |

| 2.3.3 Fluxgate Sensors                                      | 29  |

| 2.3.4 Analogue Magnetometers                                | 31  |

| 2.3.5 Digital Magnetometers                                 | 33  |

| 2.3.6 Ground Based Magnetometer Networks                    | 35  |

| 2.4 Digital Systems Design Techniques                       | 37  |

| 2.4.1 Microprocessors and DSPs                              | 39  |

| 2.4.2 Programmable Design Techniques                        | 40  |

| 2.4.2.1 Programmable Logic Devices           | 41 |

|----------------------------------------------|----|

| 2.4.3 Field Programmable Gate Arrays (FPGAs) | 41 |

| 2.4.3.1 The Xilinx VHDL Design Flow          | 43 |

| 2.4.4 FPGA Architectures                     | 45 |

| 2.4.5 Advantages of VHDL                     | 46 |

#### 3. Hardware Design of a Dual-Channel Cross-Correlator System

| 3.1 Introduction                                                             | 47 |

|------------------------------------------------------------------------------|----|

| 3.2 Auto-Correlation in Riometry                                             | 48 |

| 3.3 Cross-Correlation in Riometry                                            | 49 |

| 3.4 VHDL Modelling for the Complex Cross-Correlator                          | 50 |

| 3.5 Functional Simulation Results for the Complex Cross-Correlator           | 53 |

| 3.6 VHDL Modelling for the Complex Waveform Generator                        | 53 |

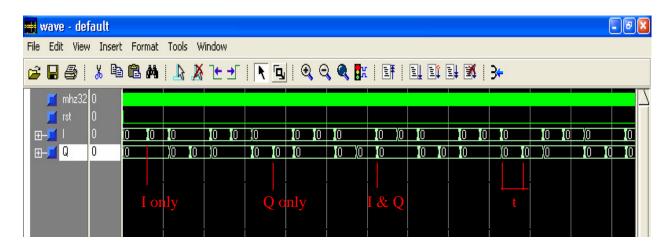

| 3.7 Functional Simulation Results for the Complex Waveform Generator         | 54 |

| 3.8 VHDL Modelling for the Direct Digital Synthesiser and Controller         | 54 |

| 3.9 Functional Simulation Results for the Digital Synthesiser and Controller | 56 |

| 3.10 VHDL Modelling for the FIFO Module and Controller                       | 56 |

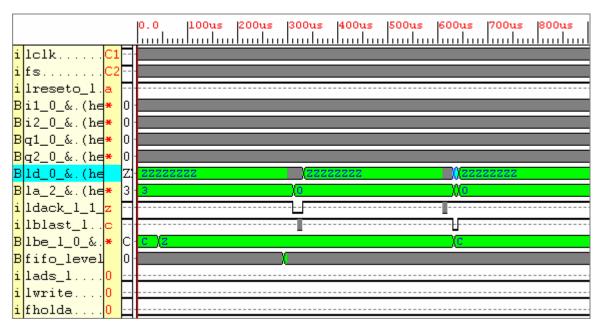

| 3.11 Functional Simulation Results for the FIFO Module and Controller        | 58 |

| 3.12 VHDL Modelling for the Frequency and Phase Controller                   | 60 |

| 3.13 Functional Simulation Results for the Frequency and Phase Controller    | 61 |

| 3.14 VHDL Modelling for the 8-Phase Dual-Channel Cross-Correlator System     | 61 |

| 3.15 Functional Simulation Results for the 8-Phase Dual-Channel              | 63 |

| Correlator System                                                            |    |

| 3.16 VHDL Modelling for the Dual-Channel Correlator System                   | 65 |

| 3.17 Functional Simulation Results for the Dual-Channel Correlator System    | 67 |

| 3.18 Hardware Implementation Results for the 8-Phase Dual-Channel            | 67 |

| Correlator System                                                            |    |

| 3.19 Timing Simulation for the 8-Phase Dual-Channel Correlator System        | 68 |

| 3.20 Hardware Implementation Results for the Dual-Channel Correlator System  | 68 |

| 3.21 Timing Simulation for the Dual-Channel Correlator System                | 69 |

| 3.22 Experimental Results for the 8-Phase Dual-Channel Correlator System     | 70 |

| 3.23 Conclusion                                                              | 71 |

| 4. PRIAMOS: RF Receiver and Peripheral Hardware Design                |     |

|-----------------------------------------------------------------------|-----|

| 4.1 Introduction                                                      | 74  |

| 4.2 Background                                                        | 75  |

| 4.3 Receiver Design Study                                             | 76  |

| 4.4 Priamos Specifications, Computer Architecture and Instrumentation | 77  |

| 4.5 RF Receiver Design                                                | 79  |

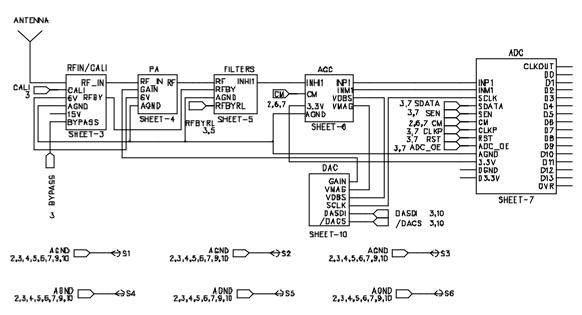

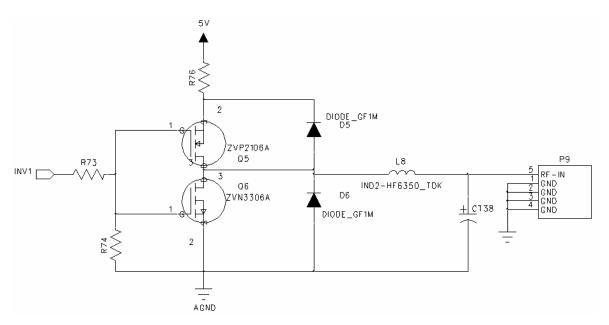

| 4.5.1 RF Input, Switching and Calibration Circuits Design             | 79  |

| 4.5.2 Pre-Amplifiers Design                                           | 80  |

| 4.5.3 Bandpass and Lowpass Filtering Design                           | 80  |

| 4.5.4 Digital Amplifier Design                                        | 81  |

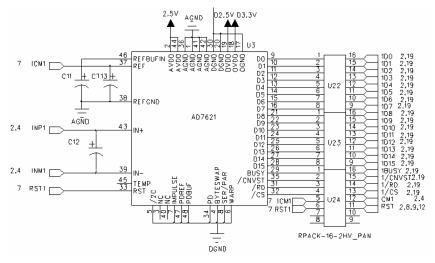

| 4.5.5 Analogue-to-Digital Converter Design                            | 82  |

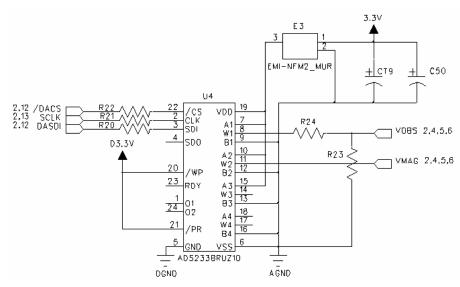

| 4.6 Peripheral Hardware Design                                        | 83  |

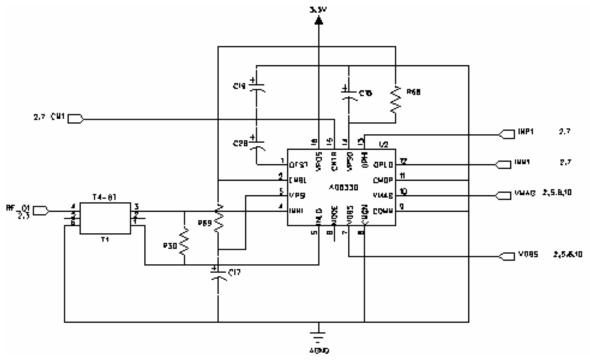

| 4.6.1 Master Oscillator Design                                        | 83  |

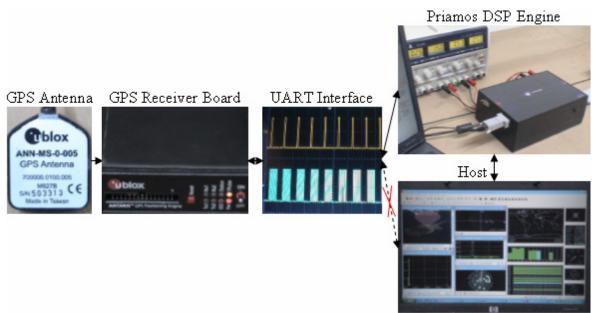

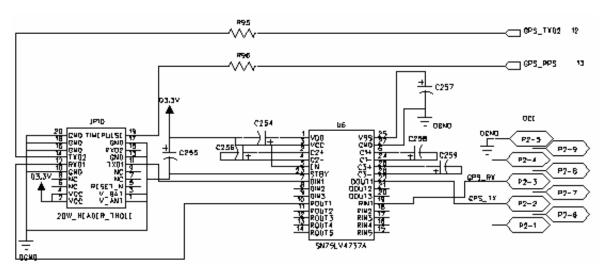

| 4.6.2 GPS Instrumentation                                             | 84  |

| 4.7 Experimental Results for the RF Receiver                          | 85  |

| 4.8 Priamos RF Receiver Unit                                          | 95  |

| 4.9 Conclusion                                                        | 95  |

| 5. PRIAMOS: DSP Engine Hardware Design                                |     |

| 5.1 Introduction                                                      | 97  |

| 5.2 Digital Finite Impulse Response Filter Design                     | 99  |

| 5.3 Digital Down Converter Selection and Modelling                    | 103 |

| 5.4 Digital Signal Processor Selection                                | 104 |

| 5.5 Prototyping Priamos using the C6416 DSK                           | 104 |

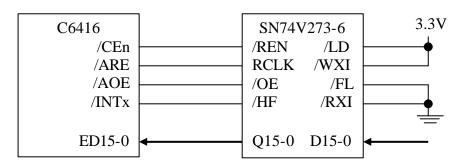

| 5.5.1 FIFO Interface Between the DDC and DSP                          | 105 |

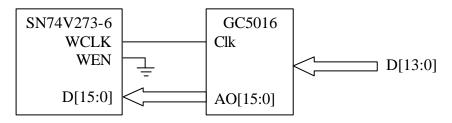

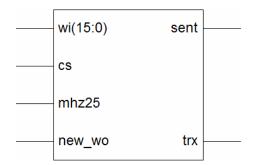

| 5.5.2 UART Data Interface                                             | 106 |

| 5.5.3 DSK-Based Priamos Prototype Considerations                      | 106 |

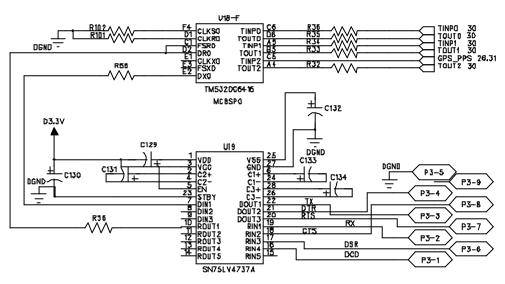

| 5.6 DSP with FPGA Co-Processor Priamos Design                         | 107 |

| 5.6.1 Software Design and Analysis                                    | 108 |

| 5.6.2 DSP with FPGA Co-Processor Design Considerations                | 109 |

| 5.7 Custom FPGA-Based Design Considerations                           | 109 |

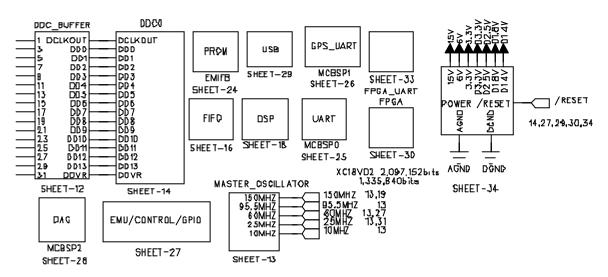

| 5.8 Priamos DSP Engine Design                                         | 109 |

| 5.8.1 Digital Down Converter Design                                   | 110 |

| 5.8.2 USB 2.0 Interface Design and Programming                        | 110 |

|    | 5.8.3 FPGA Hardware Design and Configuration                         | 111 |

|----|----------------------------------------------------------------------|-----|

|    | 5.9 Priamos DSP Engine VHDL Design                                   | 112 |

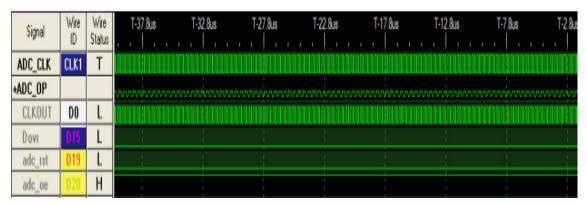

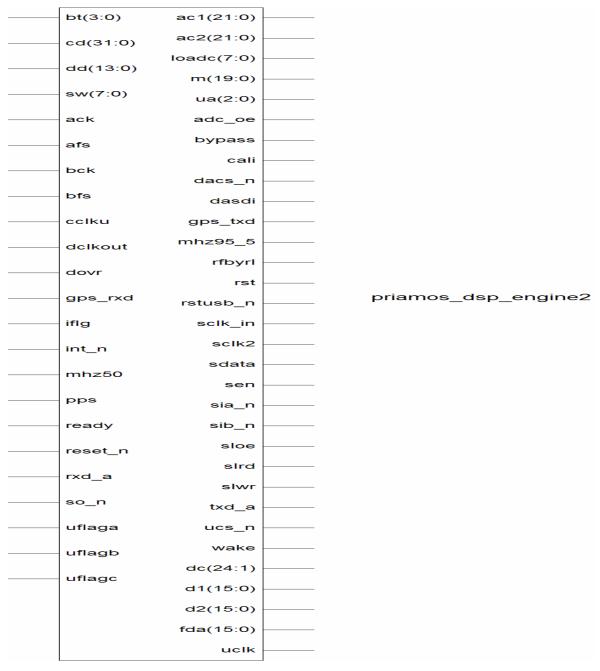

|    | 5.9.1 DDC Computer Engineering Interfaces Design                     | 113 |

|    | 5.9.2 Complex Auto-Correlator Design                                 | 117 |

|    | 5.9.3 Computer Engineering Interfaces Design                         | 117 |

|    | 5.9.4 Digital Amplifier and Analogue-to-Digital Converter Interfaces | 118 |

|    | Design                                                               |     |

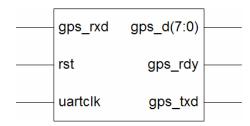

|    | 5.9.5 GPS Interface, Frequency and Master Controller Design          | 119 |

|    | 5.10 Priamos DSP Engine Unit                                         | 120 |

|    | 5.11 Conclusion                                                      | 121 |

| DI | MAGORAS: System Analysis and Sensor Design                           |     |

|    | 6.1 Introduction                                                     | 123 |

|    | 6.2 Background                                                       | 124 |

|    | 6.3 Dimagoras Specifications and Computer Architecture               | 125 |

|    | 6.4 System Analysis                                                  | 126 |

|    | 6.5 Single-Axis Sensor Design                                        | 128 |

|    | 6.6 Single-Axis Sensor Optimisation                                  | 136 |

|    | 6.7 Dual-Axis Sensor Design                                          | 143 |

|    | 6.8 Three-Axis Sensor Design and Optimisation                        | 145 |

|    | 6.9 Sensor Design Experimental Results                               | 150 |

|    | 6.10 Experimental Results for the Optimised Sensor                   | 152 |

|    | 6.11 Conclusion                                                      | 154 |

| DI | MAGORAS: Hardware Design                                             |     |

|    | 7.1 Introduction                                                     | 155 |

|    | 7.2 Pre-Amplifiers Design                                            | 156 |

|    | 7.3 Digital Amplifier Design                                         | 157 |

|    | 7.4 Analogue-to-Digital and Digital-to-Analogue Converter Design     | 157 |

|    | 7.5 Excitation Driver Power Electronics Design                       | 157 |

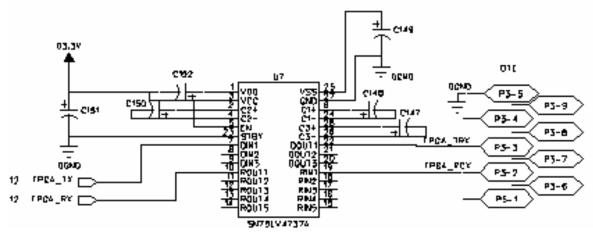

|    | 7.6 UART Interfaces Design                                           | 158 |

|    | 7.7 10/100 Mbps Fast Ethernet Interface Design                       | 158 |

|    | 7.8 16 Mbits SRAM Memory Interface Design                            | 159 |

|    | 7.9 FPGA Hardware Design and Analysis                                | 159 |

6.

7.

| 7.9.1 CIC Decimator Design                      | 162 |

|-------------------------------------------------|-----|

| 7.9.2 Power to nT Converter Design              | 164 |

| 7.9.3 Magnetic Field Total Intensity Calculator | 165 |

| 7.10 Data Logging and Data Transfer             | 165 |

| 7.11 Conclusion                                 | 166 |

#### 8. Conclusion and Future Work

| 8.1 Conclusion                                              | 167 |

|-------------------------------------------------------------|-----|

| 8.2 Further Work                                            |     |

| 8.2.1 Remodelling the Sensors using Metglas 2714A           | 169 |

| 8.2.2 Theoretical Calculation of the Earth's Magnetic Field | 170 |

| 8.2.3 VLSI Considerations for Priamos and Dimagoras         | 170 |

#### **Appendices A-E**

| Appendix A | 172 |

|------------|-----|

| Appendix B | 181 |

| Appendix C | 184 |

| Appendix D | 190 |

| Appendix E | 201 |

|            |     |

| References | 207 |

|------------|-----|

| eferences  | 207 |

## List of figures

| 2.1  | Northern Hemisphere Widebeam and Imaging Riometers.                          | 12       |

|------|------------------------------------------------------------------------------|----------|

| 2.1  | Southern Hemisphere Widebeam and Imaging Riometers.                          | 12       |

| 2.2  | Experimental and Theoretical QDCs.                                           | 16       |

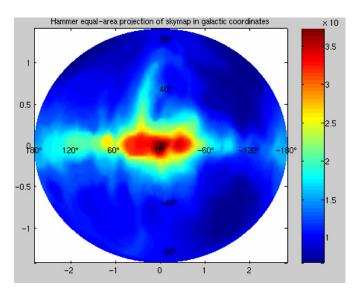

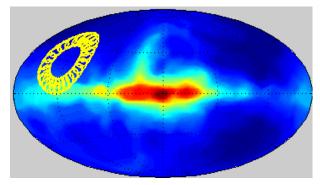

| 2.3  | Digital Sky Map at 38.2 MHz.                                                 | 17       |

| 2.5  | Right Ascension Scanning of the Galactic Plane at 38.2 MHz.                  | 18       |

| 2.6  | Cross-Dipole's Field of View at 90 Km over KIL.                              | 18       |

| 2.0  | Ionospheric Absorption.                                                      | 18       |

| 2.7  | QDCs of Auroral Absorption.                                                  | 10       |

| 2.8  | Auroral Absorption.                                                          |          |

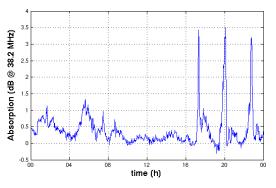

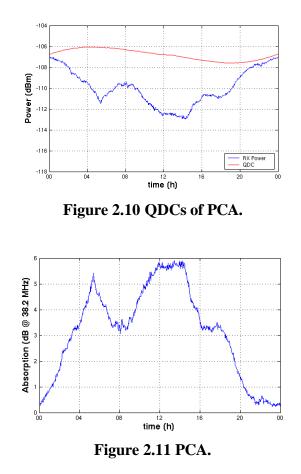

| 2.10 | QDCs of PCA.                                                                 | 19<br>20 |

| 2.10 | PCA.                                                                         | 20<br>20 |

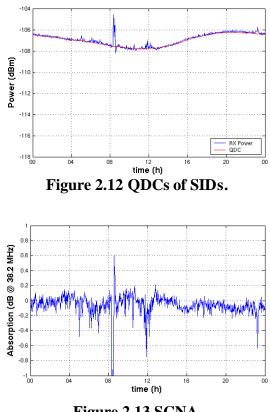

| 2.11 | QDCs of SIDs.                                                                |          |

| 2.12 | SCNA.                                                                        | 21       |

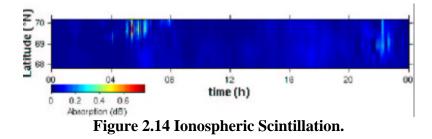

| 2.13 | Ionospheric Scintillation.                                                   | 21       |

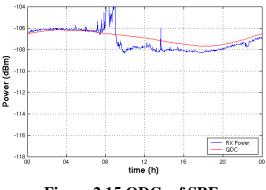

| 2.14 | QDCs of SRE.                                                                 | 22       |

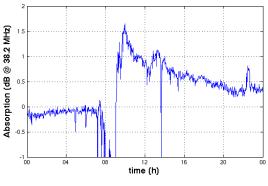

| 2.15 |                                                                              | 23       |

| 2.10 | SRE Absorption.                                                              | 23       |

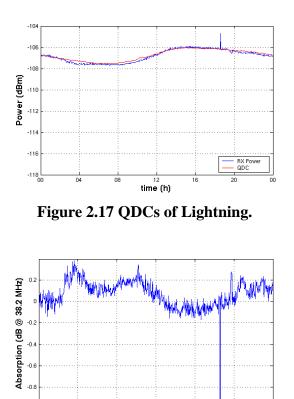

| 2.17 | QDCs of Lightning.<br>Lightning Absorption.                                  | 24       |

|      |                                                                              | 24       |

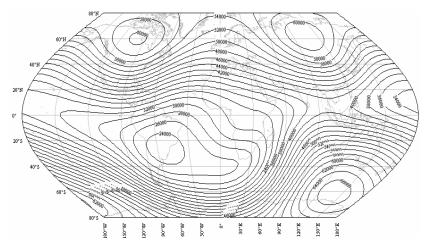

| 2.19 | Earth's Total Intensity Isodynamic Map for the 1/11/2004.                    | 26       |

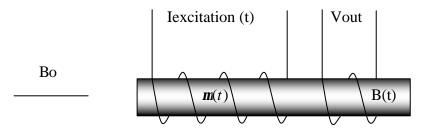

| 2.20 | The Fluxgate Principle using a Parallel Type Sensor.                         | 29       |

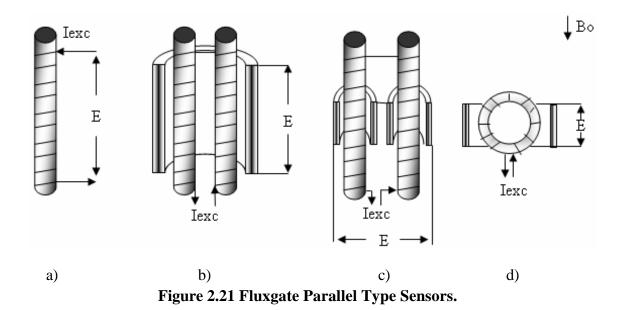

| 2.21 | Fluxgate Parallel Type Sensors.                                              | 30       |

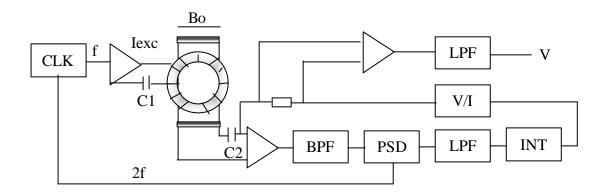

| 2.22 | 2 <sup>nd</sup> Harmonic Fluxgate Magnetometer Block Diagram.                | 31       |

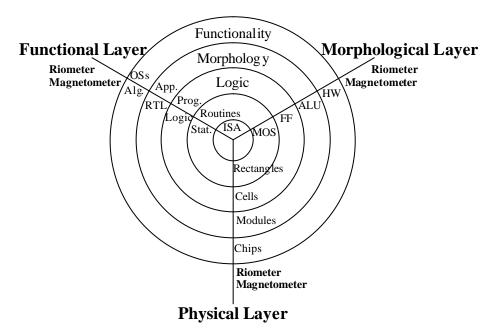

| 2.23 | Modified Gajski Y Chart.                                                     | 38       |

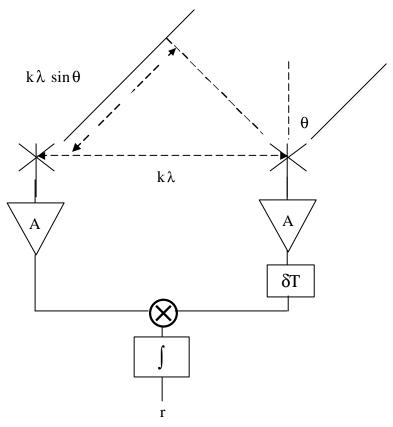

| 3.1  | Two-Element Correlated Antenna Phased-Array.                                 | 48       |

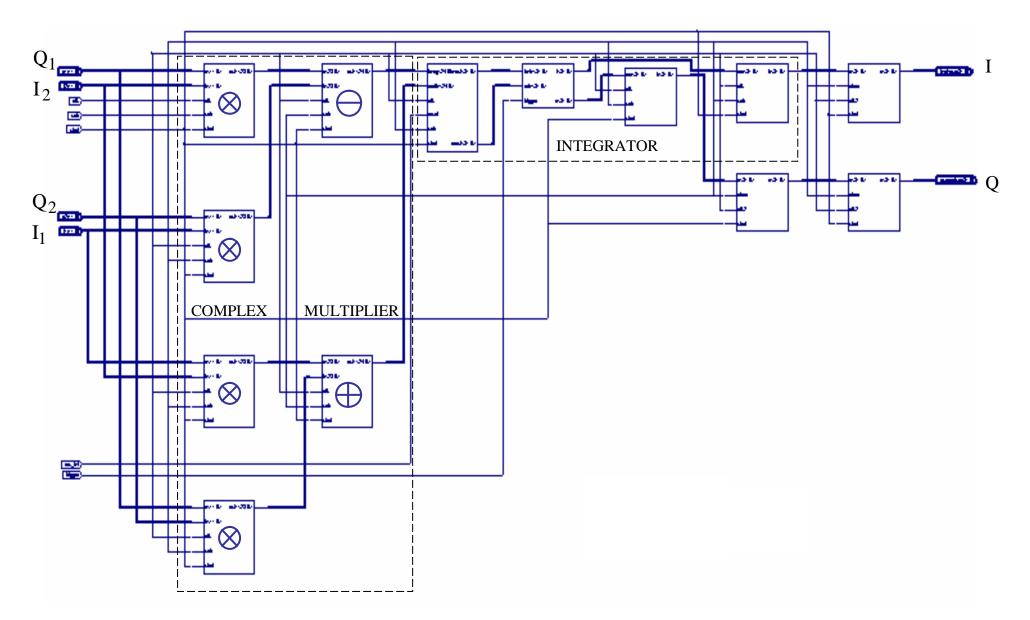

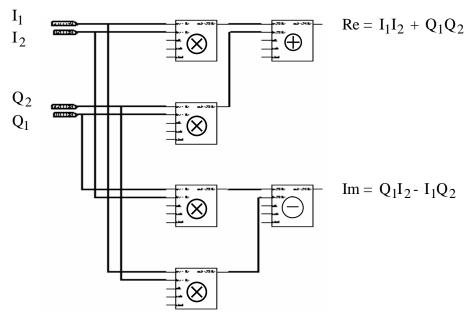

| 3.2  | Complex Multiplier's Block Diagram.                                          | 52       |

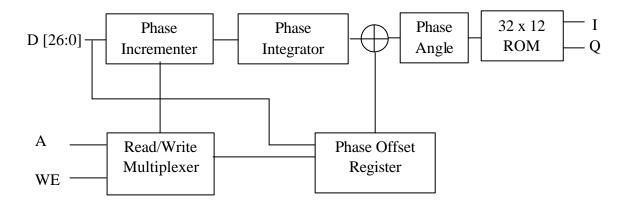

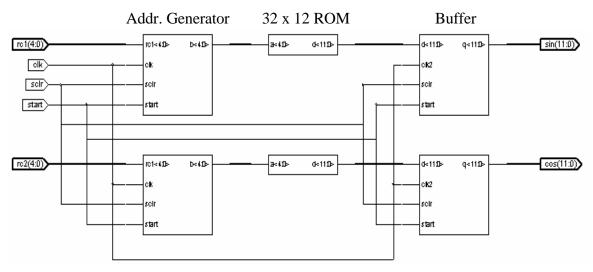

| 3.3  | DDS Block Diagram.                                                           | 54       |

| 3.4  | 8-Phase Dual-Channel Cross-Correlator System.                                | 62       |

| 3.5  | Cross-Correlator Results for the 8-Phase Auto-Switching Dual-Channel System. |          |

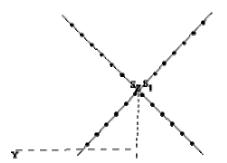

| 3.6  | Cross-Correlation Results Presented as a Rotating Vector.                    | 64       |

| 3.7  | Free-Input Dual-Channel Cross-Correlator System.                             | 66       |

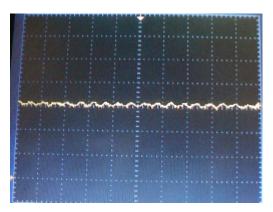

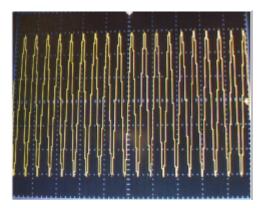

| 3.8  | Test Results for the 8-Phase Dual-Channel Correlator System.                 | 70       |

|      |                                                                              |          |

| 4.1  | The La Jolla Widebeam Riometer.                                              | 75       |

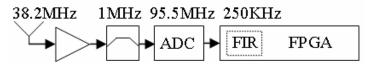

| 4.2  | IF Receiver Architecture Solution.                                           | 76       |

| 4.3  | RF Receiver Architecture Solution.                                           | 76       |

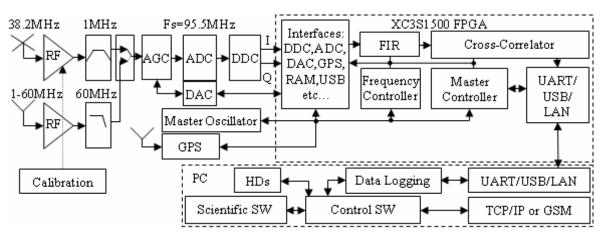

| 4.4  | Priamos Computer Architecture.                                               | 77       |

| 4.5  | Priamos Instrumentation.                                                     | 77       |

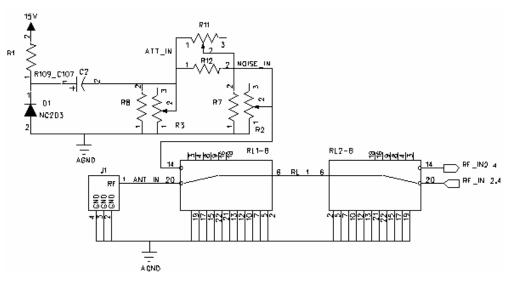

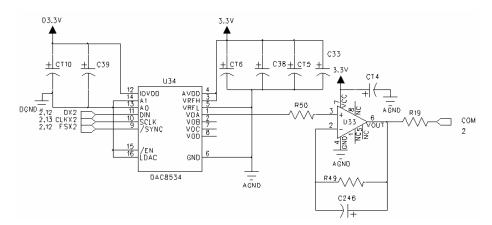

| 4.6  | Priamos RF Receiver Board Top-Level Schematic.                               | 79       |

| 4.7  | Priamos GPS Instrumentation.                                                 | 84       |

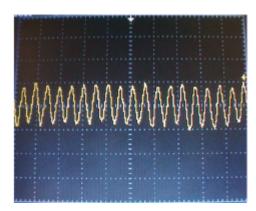

| 4.8  | Time Domain Sinewave Input to the Receiver.                                  | 85       |

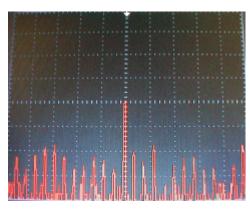

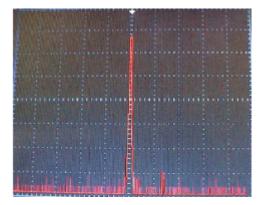

| 4.9  | Frequency Domain Sinewave Input to the Receiver.                             | 85       |

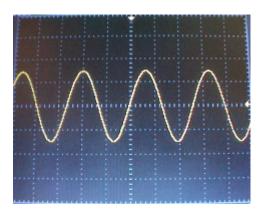

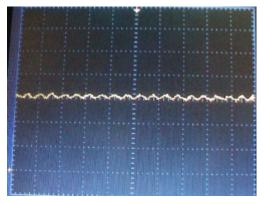

| 4.10 | Time Domain LPF Output.                                                      | 85       |

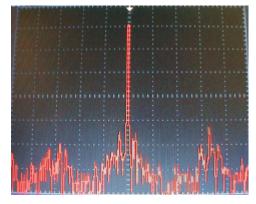

| 4.11 | Frequency Domain LPF Output.                                                 | 86       |

| 4.12 | RF Transformer LPF Output.                                                   | 86       |

| 4.13 | Common Mode Voltage.                                                         | 87       |

| 4.14 | Setting the AGC Output Swing.                                        | 87  |

|------|----------------------------------------------------------------------|-----|

| 4.15 | Setting the AGC Gain.                                                | 87  |

| 4.16 | AGC LPF Output.                                                      | 88  |

| 4.17 | ADC LPF Output.                                                      | 88  |

| 4.18 | Time Domain BPF Output.                                              | 89  |

| 4.19 | Frequency Domain BPF Output.                                         | 89  |

| 4.20 | RF Transformer BPF Output.                                           | 90  |

| 4.21 | AGC BPF Output.                                                      | 90  |

| 4.22 | ADC BPF Output.                                                      | 90  |

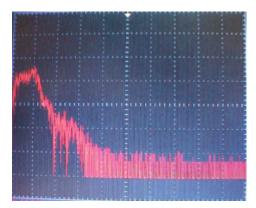

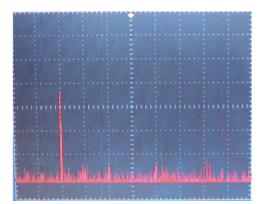

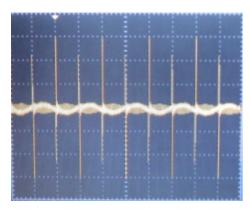

| 4.23 | NC203 Cathode Frequency Domain Response.                             | 91  |

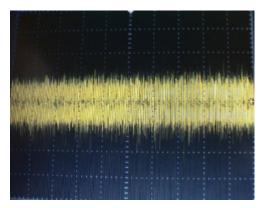

| 4.24 | NC203 Cathode Time Domain Response.                                  | 91  |

| 4.25 | Noise Circuit Time Domain Output.                                    | 91  |

| 4.26 | Frequency Domain PA Output.                                          | 92  |

| 4.27 | Frequency Domain LPF Output.                                         | 92  |

| 4.28 | RF Transformer LPF Output.                                           | 92  |

| 4.29 | RF Transformer Output.                                               | 93  |

| 4.30 | AGC LPF Output.                                                      | 93  |

| 4.31 | ADC LPF Output.                                                      | 93  |

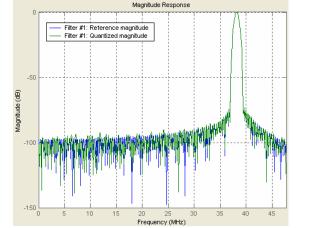

| 5.1  | Frequency Response for the Kaiser BPF (N=240).                       | 100 |

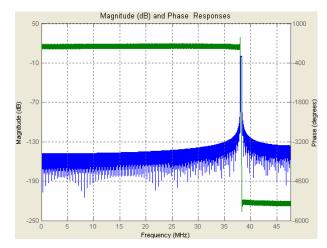

| 5.2  | BPF Frequency and Phase Response (N=9568).                           | 101 |

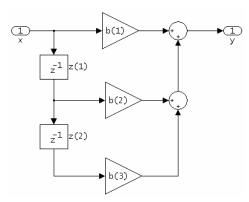

| 5.3  | Direct Form FIR BPF Implementation.                                  | 101 |

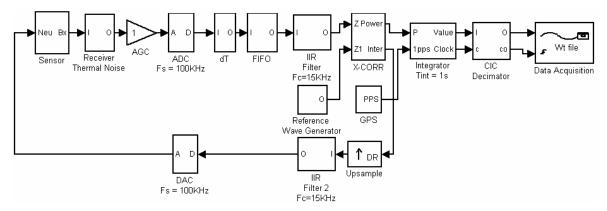

| 5.4  | Priamos Basic Simulation Model.                                      | 103 |

| 5.5  | Glueless SN74V2x5-to-EMIF Interface.                                 | 105 |

| 5.6  | DDC-to-FIFO Interface.                                               | 105 |

| 5.7  | UART Data Interface.                                                 | 106 |

| 5.8  | Priamos DSP Board Top-Level Schematic.                               | 108 |

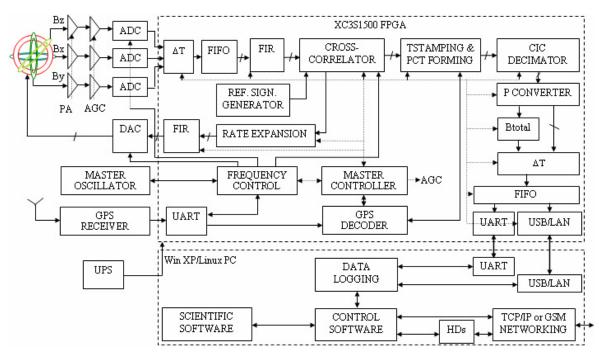

| 5.9  | Block Diagram for Priamos DSP Engine.                                | 112 |

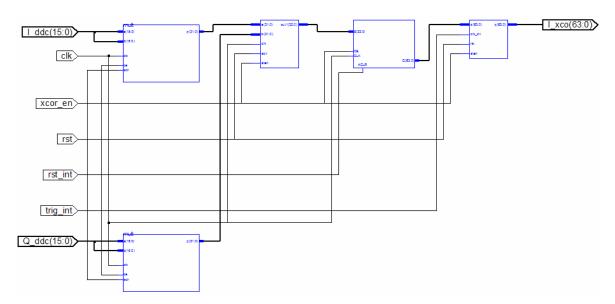

| 5.10 | Block Diagram for the DDC Interfaces.                                | 113 |

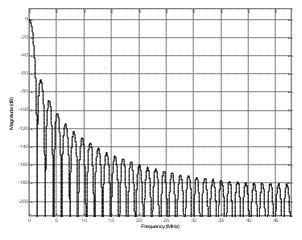

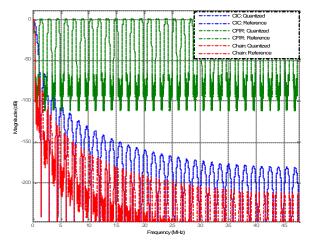

| 5.11 | CIC Filter's Frequency Response.                                     | 114 |

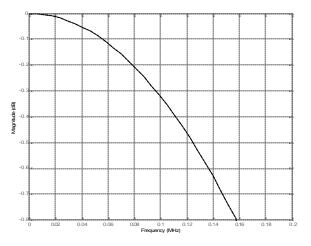

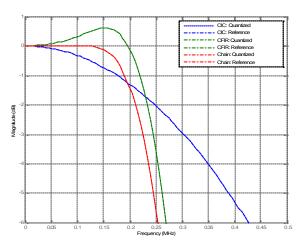

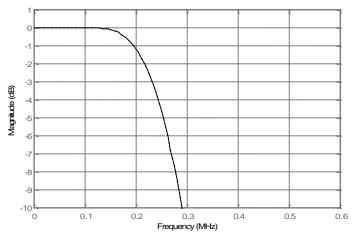

| 5.12 | CFIR Filter's Frequency Response.                                    | 114 |

| 5.13 | CIC, CFIR and Cascaded Output Frequency Response ( $f < 0.5$ MHz).   | 114 |

| 5.14 | CIC, CFIR and Cascaded Output Frequency Response (f < 50 MHz).       | 115 |

| 5.15 | PFIR Frequency Response ( $f < 0.5$ MHz).                            | 115 |

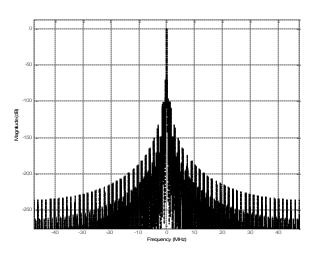

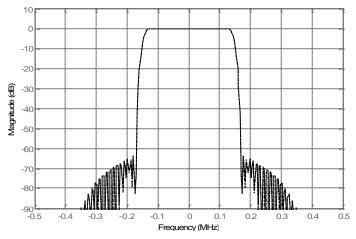

| 5.16 | Embedded DDC Frequency Response (-50 MHz < $f < 50$ MHz).            | 115 |

| 5.17 | Embedded DDC Frequency Response ( $-0.5 < f < 0.5$ MHz).             | 116 |

| 6.1  | Dimagoras Computer Architecture.                                     | 126 |

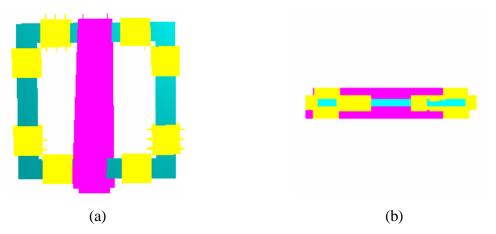

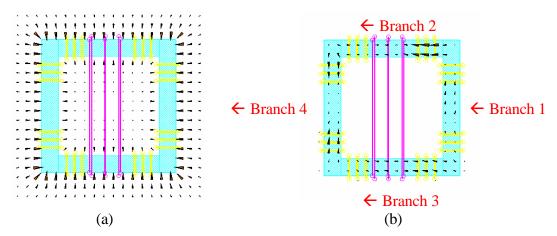

| 6.2  | (a) xy, (b) yz, Projections of the Basic Race-Track Fluxgate Sensor. | 128 |

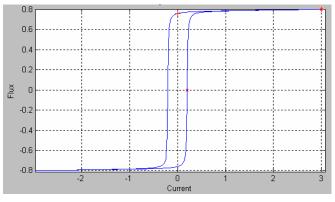

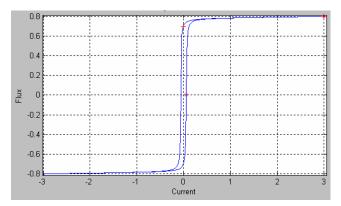

| 6.3  | Supermalloy Magnetisation B(H) Curve (T(A/m)).                       | 130 |

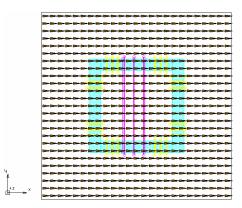

| 6.4  | X-Axis External Vector Field (1 T).                                  | 130 |

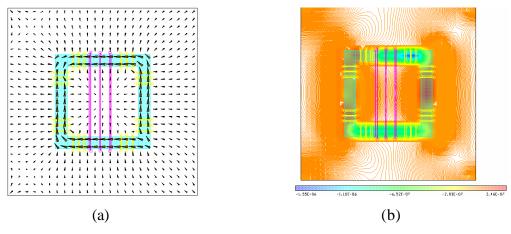

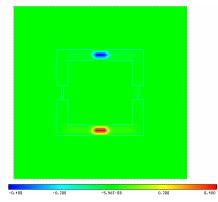

| 6.5  | (a) Arrow and (b) Contour Diagrams of B ( $Iexc = 0$ ).              | 130 |

| 6.6  | (a) Arrow and (b) Contour Diagrams of B at Magnetic Saturation.      | 131 |

| 6.7  | (a) Permeability Distribution at Magnetic Saturation,                | 131 |

|      | (b) Maxwell Stress and Lorentz Force Distribution.                   |     |

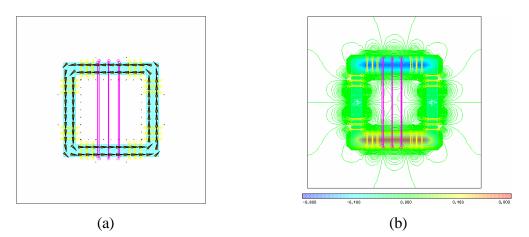

| 6.8  | Dimagoras Matlab Simulink Model.                                     | 134 |

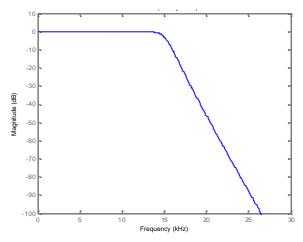

| 6.9  | FIR LPF Filter Frequency Response.                                   | 134 |

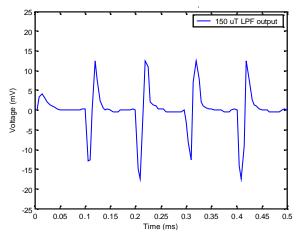

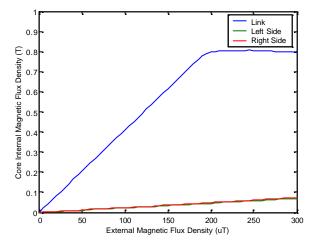

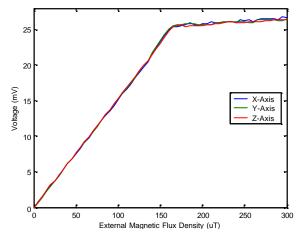

| 6.10 | Sensor's Output Response for $B = 150 \text{ uT}$ .                  | 134 |

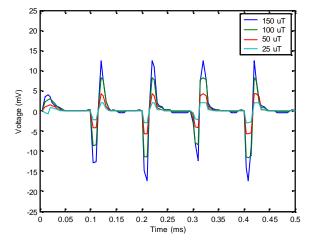

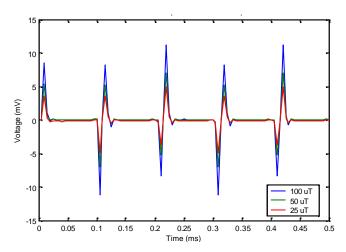

| 6.11 | Sensor's Output Response for $B = 25, 50, 100$ and 150 uT.           | 135 |

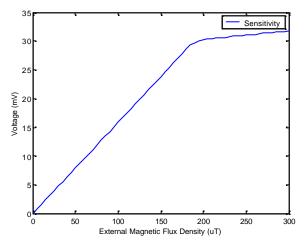

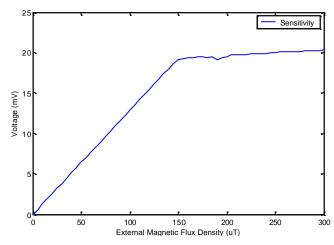

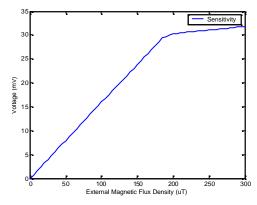

| 6.12 | Sensor's Sensitivity Diagram.                                        | 135 |

| 6.13 | (a) External Field (b) External Field Flow Through the Core                      | 136 |

|------|----------------------------------------------------------------------------------|-----|

| 614  | at Premagnetisation.                                                             | 127 |

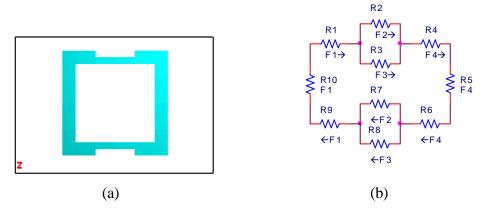

| 6.14 | (a) Modified Core (b) Flux Flow Through the Modified Core.                       | 137 |

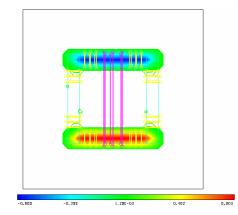

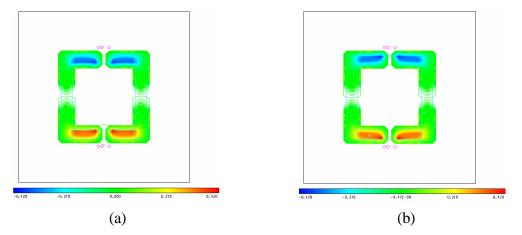

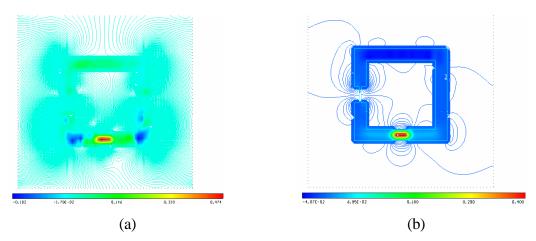

| 6.15 | Supermalloy Core at Saturation ( $B = 0.8$ T, Iexc = 250 mA).                    | 139 |

| 6.16 | Magnetic Flux Density Distribution ( $B = 0.3$ T, Iexc = 60 mA).                 | 139 |

| 6.17 | Magnetic Flux Density Distribution (B = $0.42$ T, Iexc = $60$ mA).               | 140 |

| 6.18 | (a) $B = 0.21$ T, $Iexc = 60$ mA (b) $B = 0.207$ T, $Iexc = 60$ mA.              | 140 |

| 6.19 | (a) $B = 0.4$ T, Iexc = 60 mA (b) $B = 0.68$ T, Iexc = 60 mA.                    | 140 |

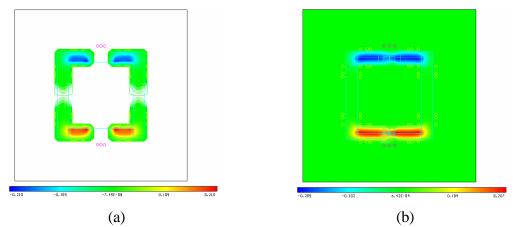

| 6.20 | B Distribution (Bsat = $0.8$ T, Iexc = $60$ mA).                                 | 141 |

| 6.21 | Optimised Sensor's Sensitivity Diagram for Bottom x-Branch.                      | 141 |

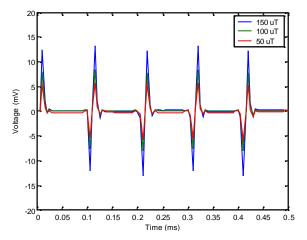

| 6.22 | Sensor's Output Response for $B = 25$ , 50 and 100 uT.                           | 141 |

| 6.23 | Optimised Sensor's Sensitivity Diagram.                                          | 142 |

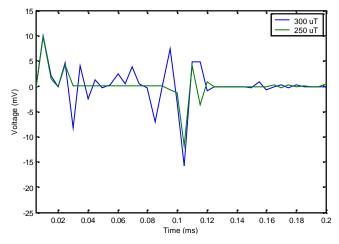

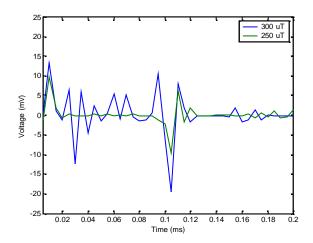

| 6.24 | Sensor's Output Response for $B = 250$ and 300 uT.                               | 142 |

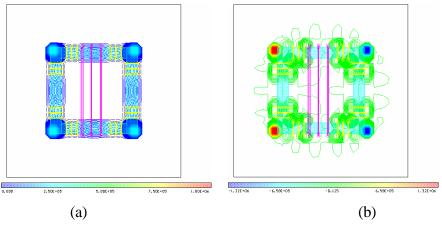

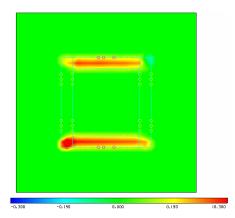

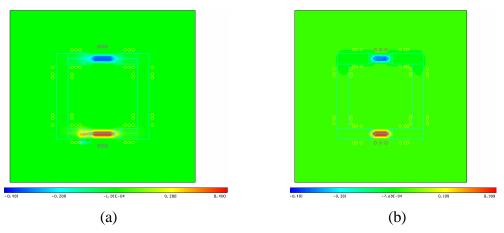

| 6.25 | X-Axis Magnetic Flux Density Distribution ( $B = 0.4 \text{ T}$ , Iexc = 60 mA). | 143 |

| 6.26 | Magnetic Flux Density Distribution (a) $Bsat = 0.474 T$ (b) $B = 0.408 T$ .      | 143 |

| 6.27 | Magnetic Flux Density Distribution (Bsat = $0.468$ T).                           | 144 |

| 6.28 | Magnetic Flux Density Distribution (Bsat = $0.8$ T, Iexc = $1.4$ mA).            | 144 |

|      | (a) 3-Dimensional Model (b) z-Cut Cross-Section.                                 |     |

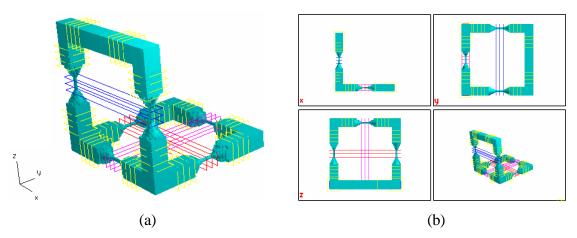

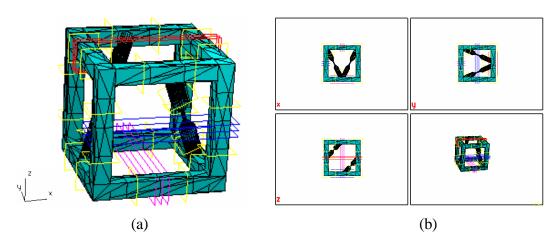

| 6.29 | Basic 3-Dimensional Sensor (a) 3-D Model (b) XYZ Projections.                    | 145 |

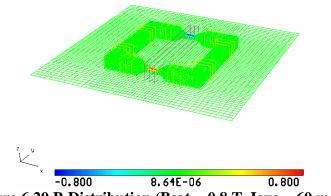

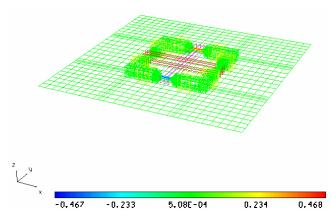

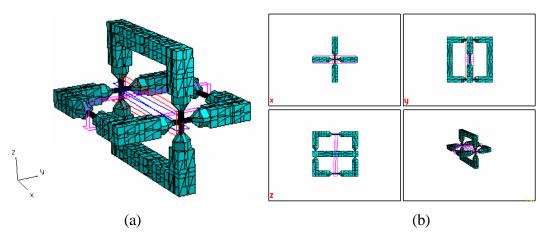

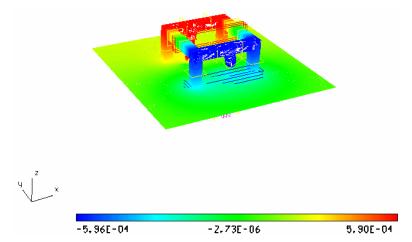

| 6.30 | Magnetic Flux Density Distribution (Bsat = $0.8$ T, Iexc = $35$ uA).             | 145 |

| 6.31 | 3-Dimensional Sensor No. 2 (a) 3-D Model (b) XYZ Projections.                    | 145 |

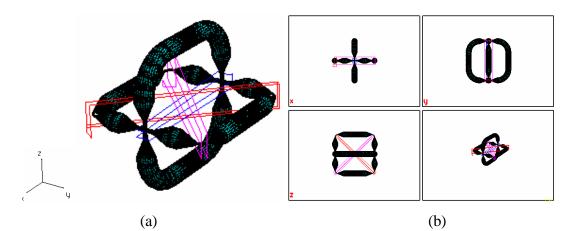

| 6.32 | 3-Dimensional Sensor No. 3 (a) 3-D Model (b) XYZ Projections.                    | 146 |

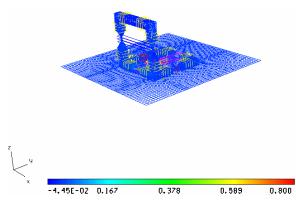

| 6.33 | 3-Dimensional Sensor Final Design (a) 3-D Model (b) XYZ Projections.             | 146 |

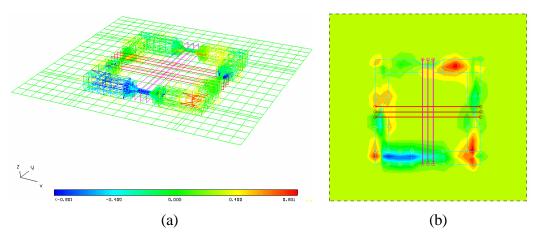

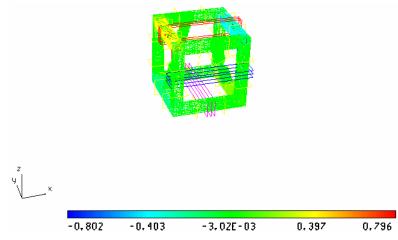

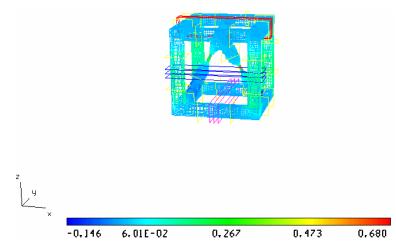

| 6.34 | 3-D Sensor B Distribution (Bsat = $0.8$ T, Iexc = $60$ mA).                      | 147 |

| 6.35 | 3-D Him Phase Distribution.                                                      | 147 |

| 6.36 | Magnetic Flux Density Distribution (Bsat = $0.68$ T).                            | 147 |

| 6.37 | 3-D Sensor's Sensitivity Diagram.                                                | 148 |

| 6.38 | 3-D Sensor's Output Response for $B = 50$ , 100 and 150 uT.                      | 148 |

| 6.39 | 3-D Sensor's Output Response at Saturation for $B = 250$ and 300 uT.             | 148 |

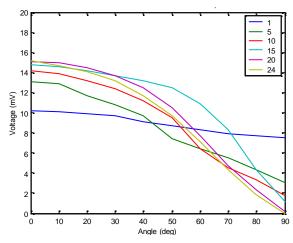

| 6.40 | 3-D Sensor's Directivity Diagram for $B = 100 \text{ uT}$ .                      | 149 |

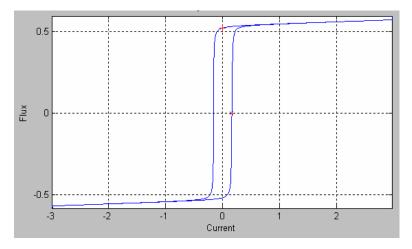

| 6.41 | Tri-Axial Sensor's Magnetisation B(H) Curve (T(A/m)).                            | 149 |

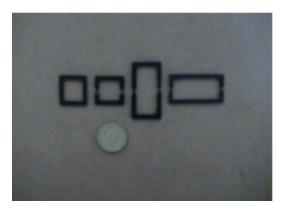

| 6.42 | Prototype Fluxgate Sensor Cores.                                                 | 150 |

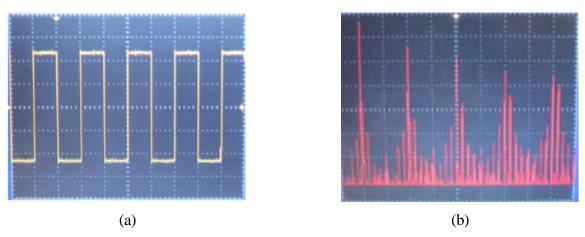

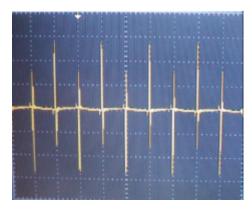

| 6.43 | Excitation Waveform in (a) Time (b) Frequency Domain.                            | 150 |

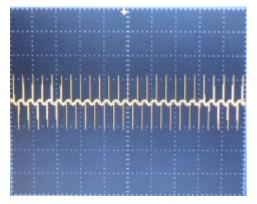

| 6.44 | Driving the Sensor within the Linear Magnetisation Region.                       | 151 |

| 6.45 | LPF Frequency Response.                                                          | 151 |

| 6.46 | Sensor's Output Response for $B = 60 \text{ uT}$ .                               | 151 |

| 6.47 | Sensor's Sensitivity Diagram.                                                    | 152 |

| 6.48 | Core Excitation from Premagnetisation to +/- Magnetic Saturation.                | 152 |

| 6.49 | Sensor's Output Response for $B = 60 \text{ uT}$ .                               | 153 |

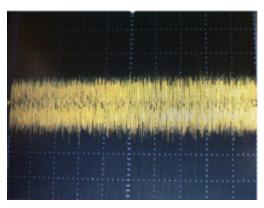

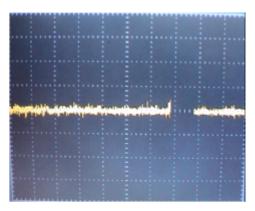

| 6.50 | Frequency Domain Noise Spectrum for the Optimised Sensor.                        | 153 |

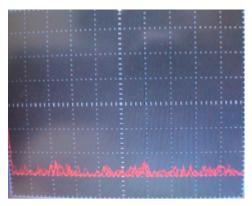

| 6.51 | Time Domain Noise Spectrum for the Optimised Sensor.                             | 153 |

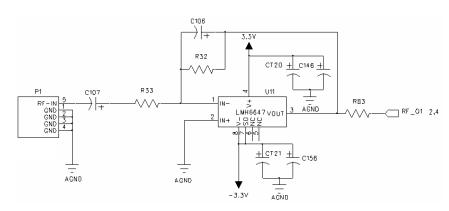

| 7.1  | PA Schematic.                                                                    | 156 |

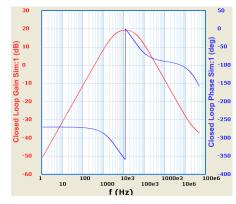

| 7.2  | PA Frequency and Phase Response.                                                 | 156 |

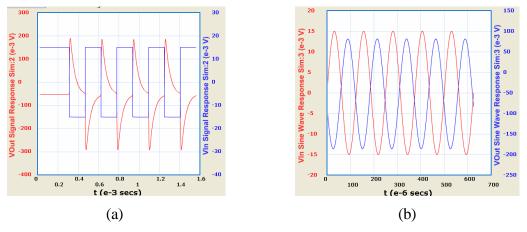

| 7.3  | PA Response for a (a) Squarewave or (b) Sinewave Input.                          | 156 |

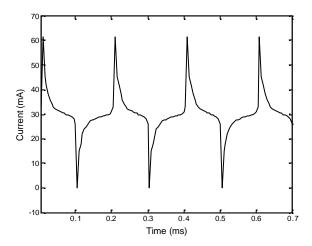

| 7.4  | Excitation Coil Saturation Current.                                              | 157 |

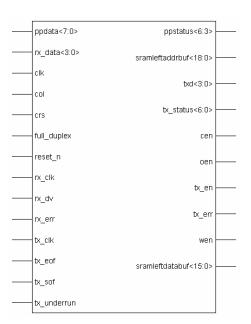

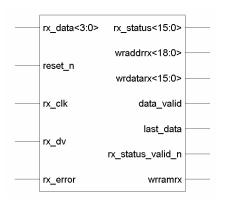

| 7.5  | Block Diagram for the 10/100 Mbps Fast Ethernet Interface.                       | 159 |

| 7.6  | Block Diagram for the Ethernet Receiver.                                         | 159 |

| 7.7  | Block Diagram for the Ethernet Transmitter.                                      | 159 |

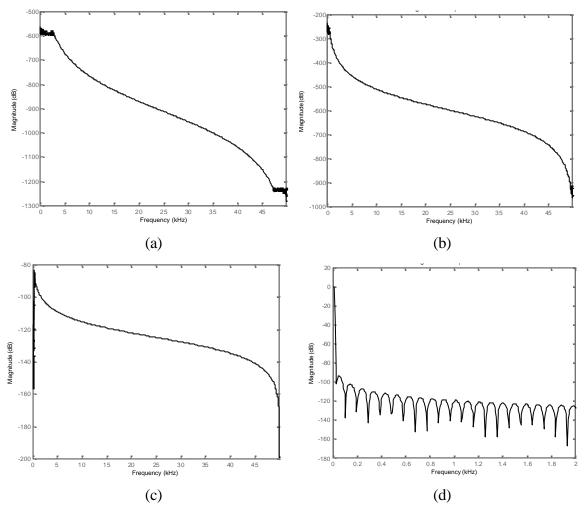

| 7.8          | <ul><li>(a) IIR Butterworth (b) IIR Chebyshev I (c) IIR Chebyshev II</li><li>(d) FIR Kaiser, LPF Frequency Response (BW = 10 Hz).</li></ul> | 162 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

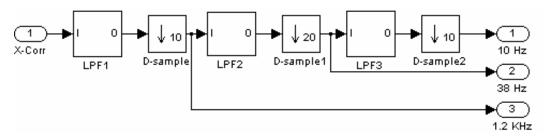

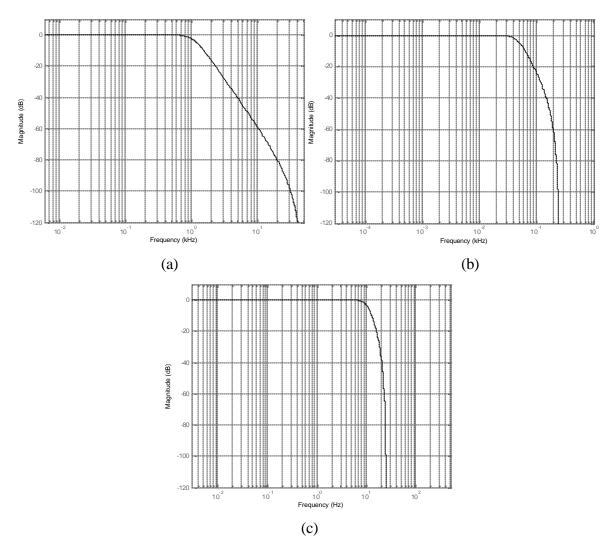

| 7.9          | 3-Stage Decimator Design.                                                                                                                   | 163 |

| 7.10         | Decimator's Bode Plot for (a) 1.2 KHz (b) 38 Hz (c) 10 Hz BW O/Ps.                                                                          | 163 |

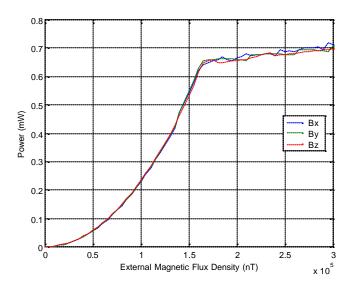

| 7.11         | Power to nT Curves for the 3-D Sensor.                                                                                                      | 164 |

| 8.1          | Metglas 2714A Magnetisation B (H) Curve (T(A/m)).                                                                                           | 169 |

| A.1          | Complex Cross-Correlator's Block Diagram.                                                                                                   | 172 |

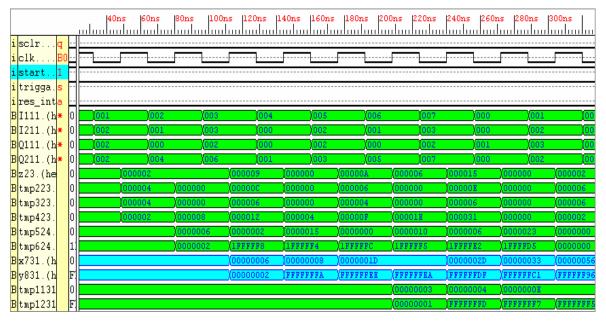

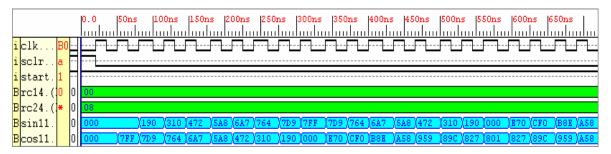

| A.2          | Functional Simulation Results for the Cross-Correlator.                                                                                     | 172 |

| A.3          | Block Diagram of the Complex-Waveform Generator.                                                                                            | 173 |

| A.4          | Functional Simulation Results for the Complex-Waveform Generator.                                                                           | 173 |

| A.5          | Results for the 1 <sup>st</sup> Channel DDS and Controller.                                                                                 | 173 |

| A.6          | Results for the 2 <sup>nd</sup> Channel DDS and Controller.                                                                                 | 173 |

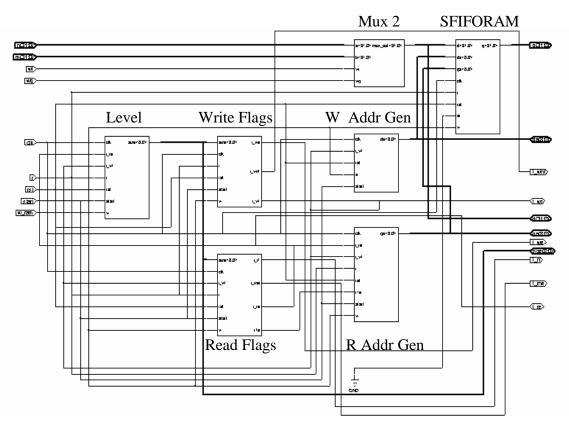

| A.7          | Block Diagram of the FIFO Module and Controller.                                                                                            | 174 |

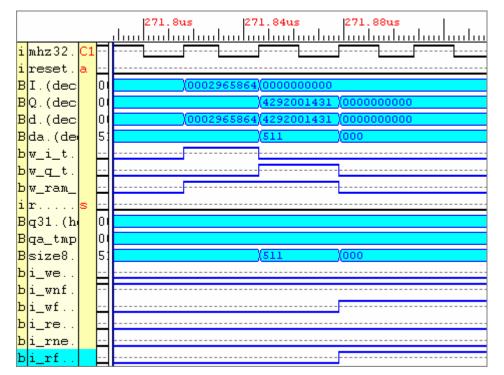

| A.8          | Beginning of Write Cycle Results for the Cross-Correlator, FIFO and FIFO Controller.                                                        | 174 |

| A.9          | End of Write Cycle Results for the X-Correlator, FIFO and FIFO Controller.                                                                  | 175 |

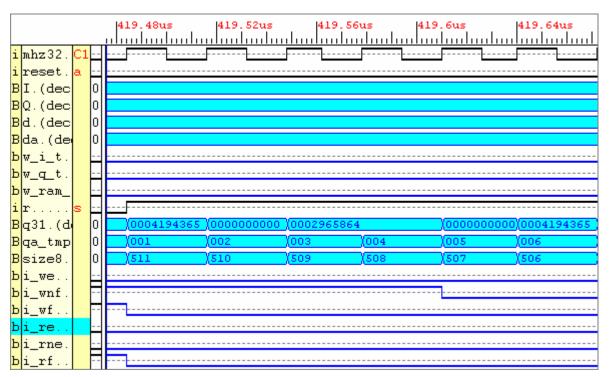

| A.10         | Beginning of Read Cycle Results for the Cross-Correlator, FIFO and FIFO Controller.                                                         | 175 |

| A.11         | End of Read Cycle Results for the Cross-Correlator, FIFO and FIFO Controller.                                                               | 176 |

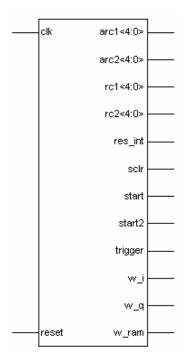

| A.12         | Block Diagram for the Frequency and Phase Controller.                                                                                       | 176 |

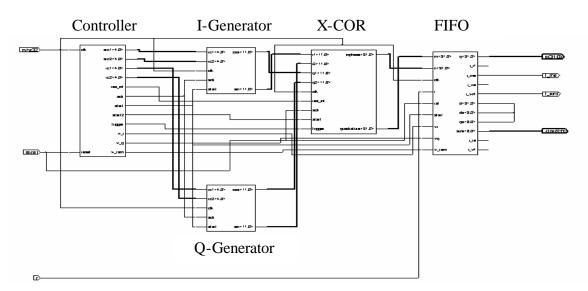

| A.13         | Block Diagram for Controller, I & Q Generator, X-COR and FIFO.                                                                              | 177 |

| A.14         | Functional Simulation Results for the Frequency and Phase Controller.                                                                       | 177 |

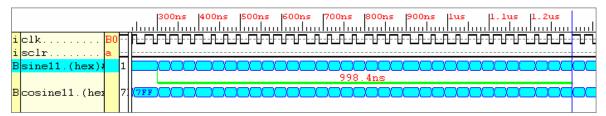

| A.15         | Functional Simulation Results for the 8-Phase Auto-Switching Dual-Channel Correlator.                                                       | 178 |

| A.16         | Functional Simulation Results for the Dual-Channel Correlator System.                                                                       | 178 |

| A.17         | 8-Phase Auto-Switching Dual-Channel Correlator Design Summary.                                                                              | 179 |

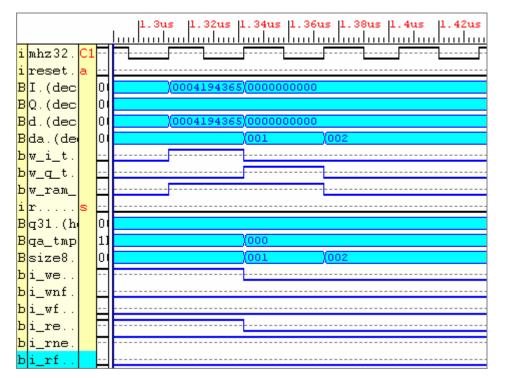

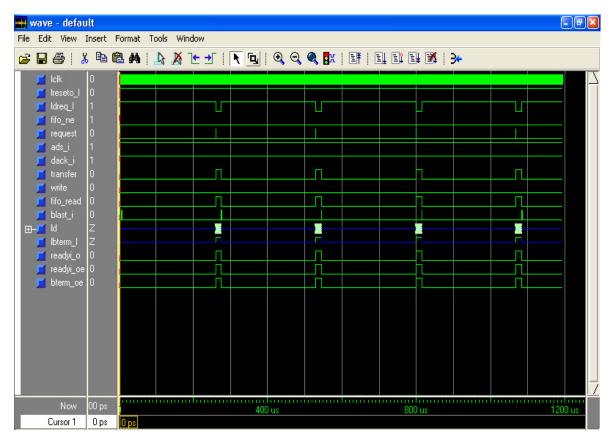

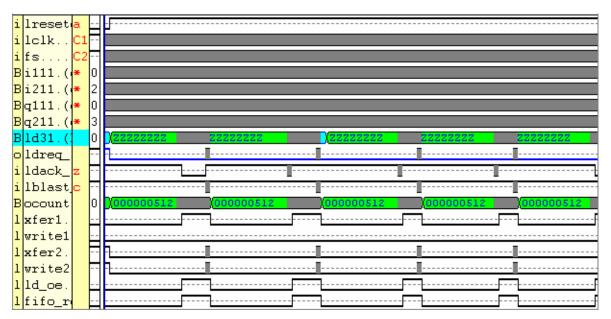

| A.18         | Timing Simulation Results for the 8-Phase Dual-Channel Correlator System.                                                                   | 179 |

| A.19         | 8-Phase Auto-Switching Dual-Channel Correlator Design Summary.                                                                              | 180 |

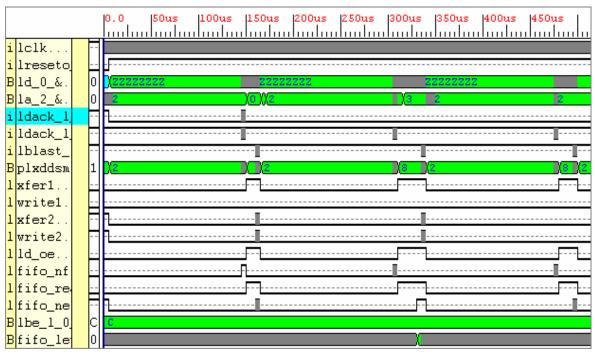

| A.20         | Timing Simulation Results for the Dual-Channel Correlator System.                                                                           | 180 |

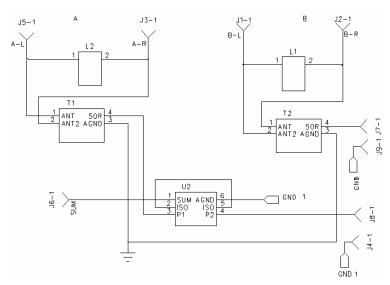

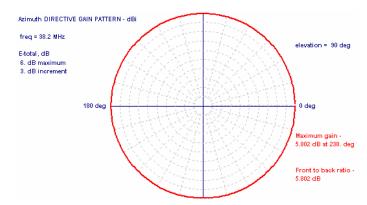

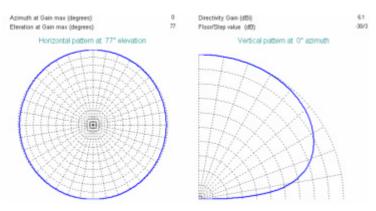

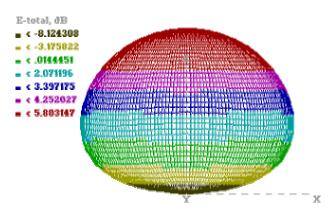

| B.1          | Crossed-Dipole Antenna Modelling.                                                                                                           | 181 |

| B.2          | Crossed-Dipole Antenna PCB Schematic.                                                                                                       | 182 |

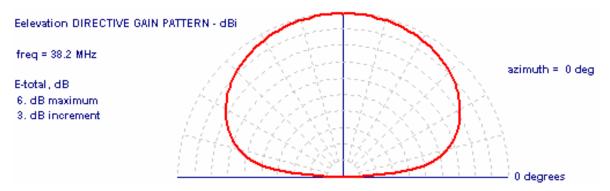

| B.3          | Crossed-Dipole Vertical Pattern.                                                                                                            | 182 |

| B.4          | Crossed-Dipole Horizontal Pattern Maximum Gain Elevation.                                                                                   | 183 |

| B.5          | HX950 Horizontal and Elevation Patterns.                                                                                                    | 183 |

| B.6          | 3-D Crossed Dipole Radiation Pattern.                                                                                                       | 183 |

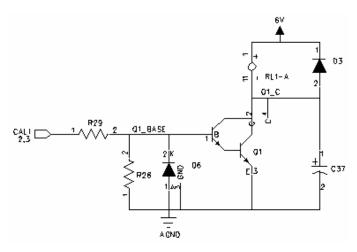

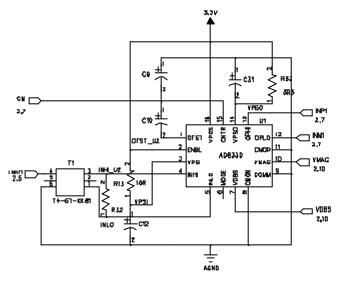

| C.1          | RF Input, Switching and Calibration Schematic.                                                                                              | 184 |

| C.2          | RF Relays' Control Schematic.                                                                                                               | 184 |

| C.3          | PA Schematic.                                                                                                                               | 184 |

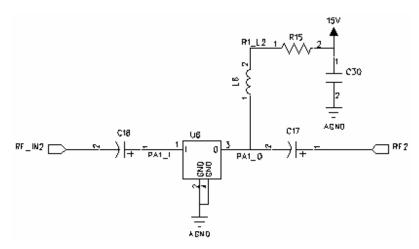

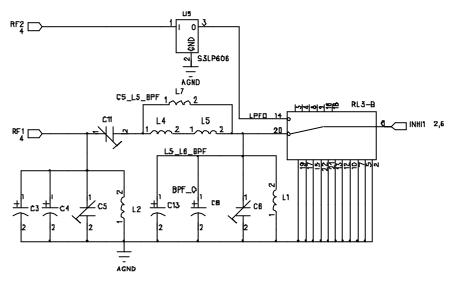

| C.4          | BPF and LPF Schematic.                                                                                                                      | 185 |

| C.5          | AGC Schematic.                                                                                                                              | 185 |

| C.6<br>C.7   | Digital Potentiometer Schematic.<br>ADC Schematic.                                                                                          | 185 |

|              |                                                                                                                                             | 186 |

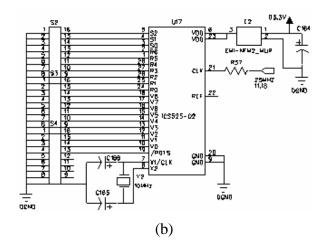

| C.8<br>C.9   | Master Oscillator Schematic (a) & (b).                                                                                                      | 186 |

| C.9<br>C.10  | ADC BPF Output.                                                                                                                             | 187 |

| C.10<br>C.11 | ADC Output during Saturation.                                                                                                               | 187 |

| U.11         | Auto-Recovery from Saturation.                                                                                                              | 187 |

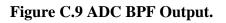

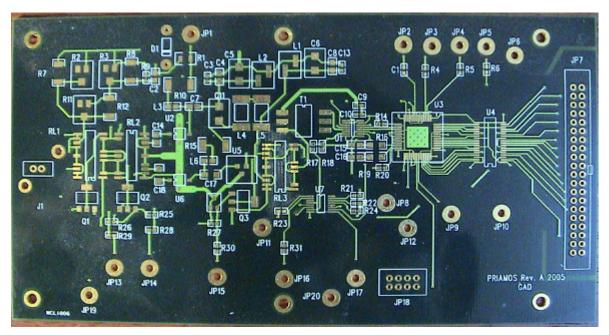

| C.12<br>C.13 | 4-Layer Priamos Antenna PCB Top-Side.<br>4-Layer Priamos Antenna PCB Bottom-Side. | 188<br>188 |

|--------------|-----------------------------------------------------------------------------------|------------|

| C.13<br>C.14 | Priamos RF Receiver Unit.                                                         | 188        |

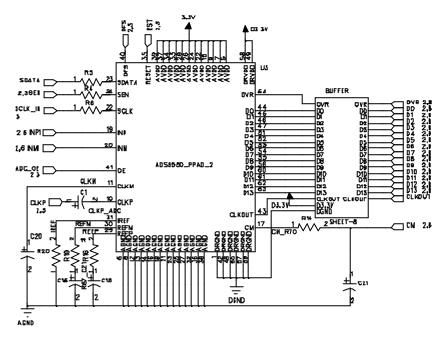

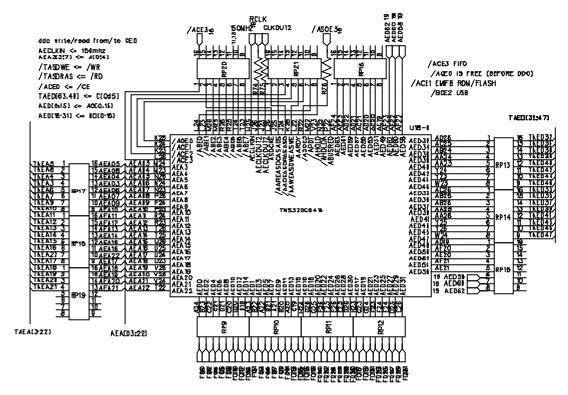

| D.1          | DSP EMIF A Schematic.                                                             | 190        |

| D.2          | FPGA Co-Processor.                                                                | 190        |

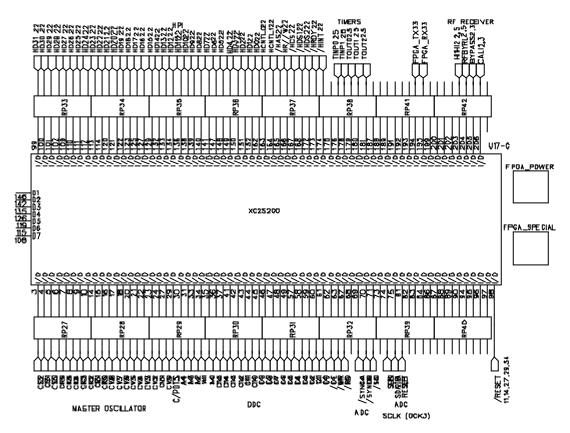

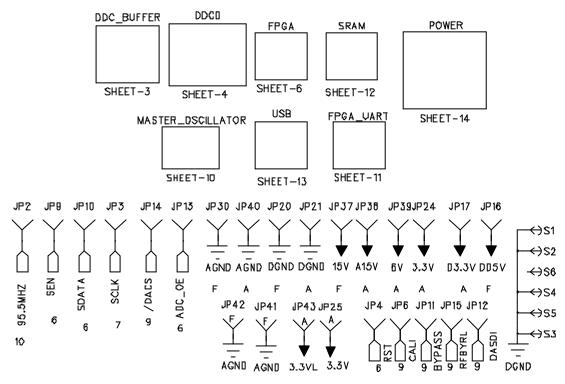

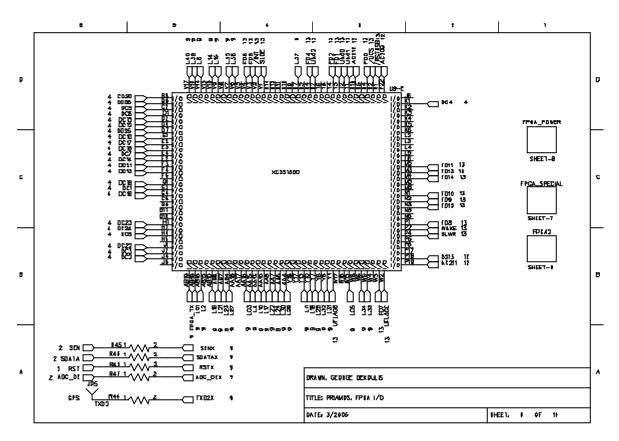

| D.3          | (a) DSP- (b) FPGA-Based Schematic Contents.                                       | 191        |

| D.4          | Priamos DSP Engine Board Top-Level Schematic.                                     | 191        |

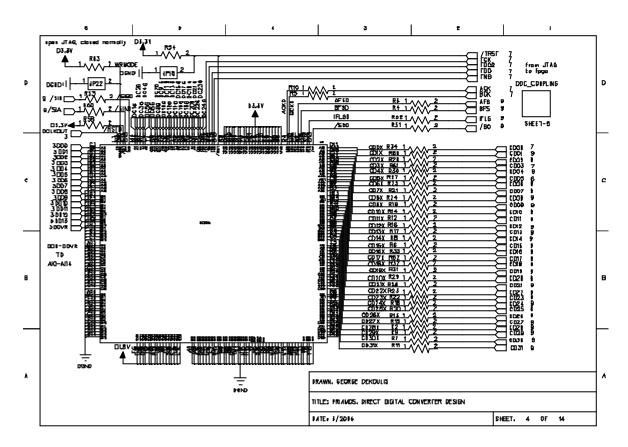

| D.5          | DDC Circuit Schematic.                                                            | 192        |

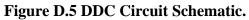

| D.6          | USB 2.0 Interface Schematic.                                                      | 192        |

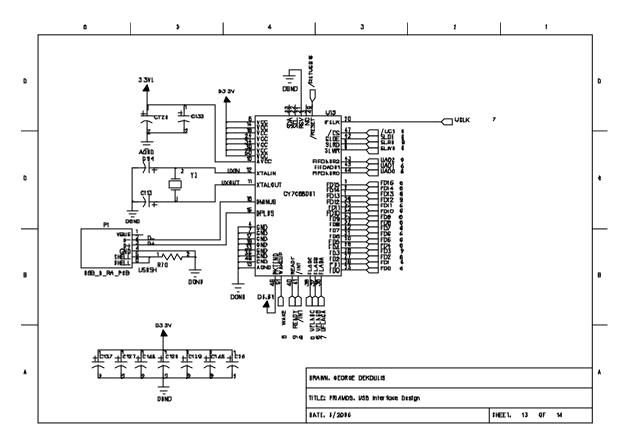

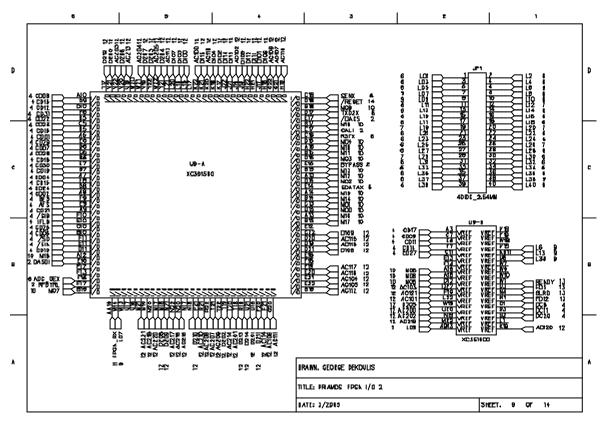

| D.7          | FPGA I/O Circuit Schematic 1.                                                     | 193        |

| D.8          | FPGA I/O Circuit Schematic 2.                                                     | 193        |

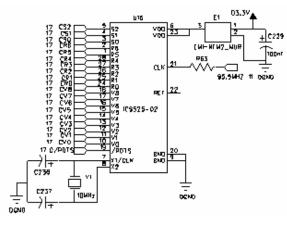

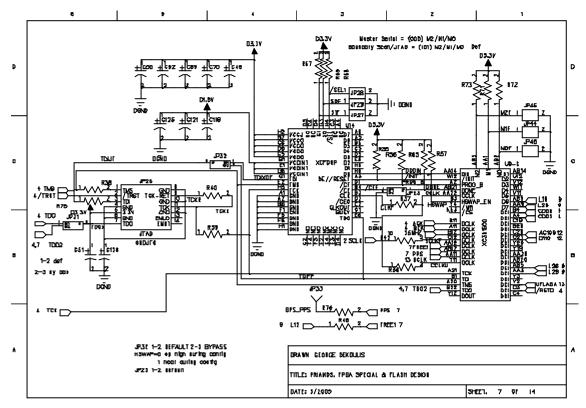

| D.9          | FPGA Programming and Special I/O Circuit Schematic.                               | 194        |

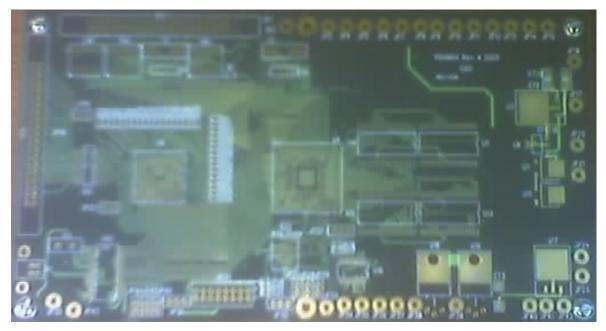

| D.10         | 6-Layer Priamos DSP Engine PCB Top-Side.                                          | 194        |

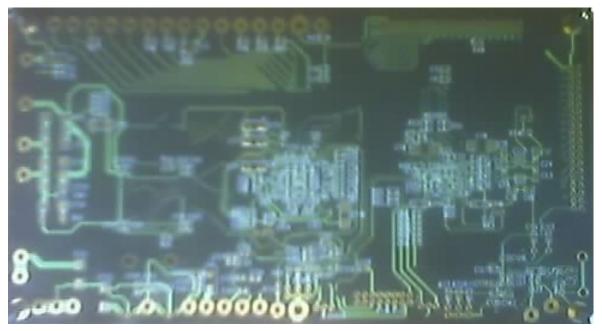

| D.11         | 6-Layer Priamos DSP Engine PCB Bottom-Side.                                       | 195        |

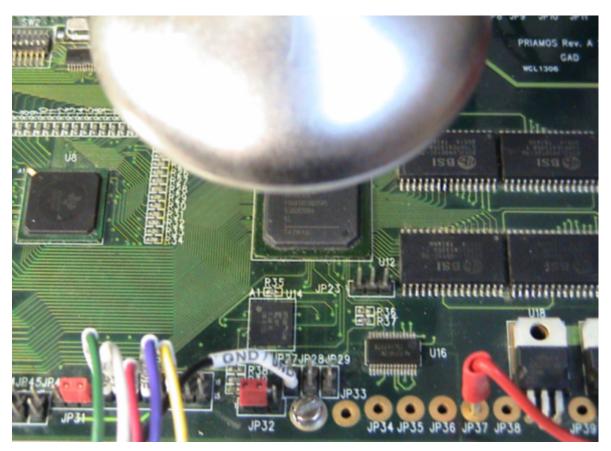

| D.12         | DSP Engine Early Prototype Testing.                                               | 195        |

| D.13         | Priamos DSP Engine FPGA Computer Architecture.                                    | 196        |

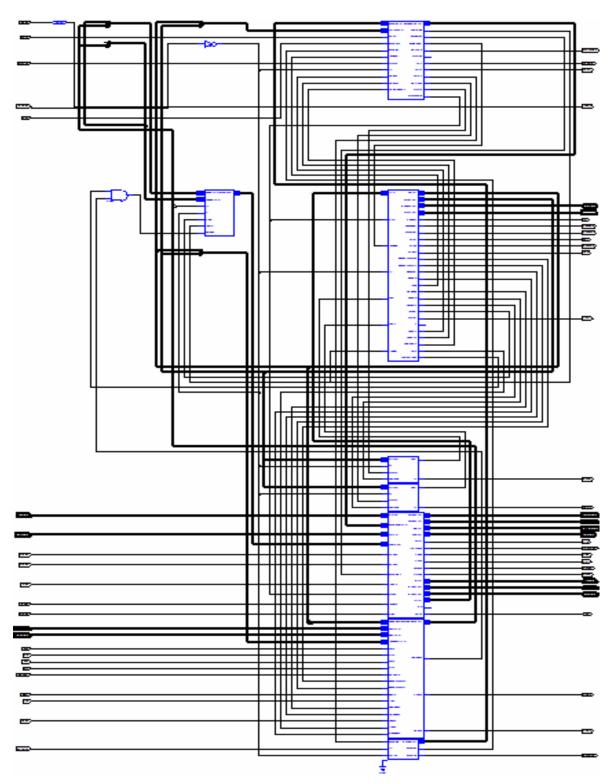

| D.14         | Auto-Correlator Computer Architecture.                                            | 197        |

| D.15         | Block Diagram for the Computer Engineering Interfaces.                            | 197        |

| D.16         | Block Diagram for the Digital Amplifier Interface.                                | 197        |

| D.17         | Block Diagram for the GPS Interface.                                              | 198        |

| D.18         | Block Diagram for the Frequency Controller.                                       | 198        |

| D.19         | Priamos DSP Engine Design Summary.                                                | 199        |

| D.20         | Priamos DSP Engine Unit.                                                          | 200        |

| E.1          | Automatic Gain Controller Schematic.                                              | 201        |

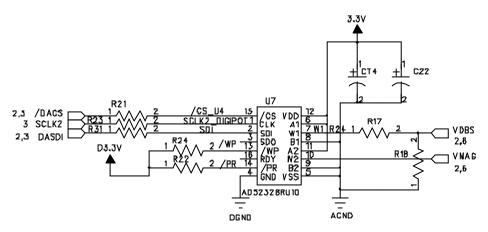

| E.2          | Digital Potentiometer Schematic.                                                  | 201        |

| E.3          | ADC Schematic.                                                                    | 202        |

| E.4          | DAC Schematic.                                                                    | 202        |

| E.5          | Power Inverter Schematic.                                                         | 202        |

| E.6          | GPS to FPGA, UART Interface Schematic.                                            | 203<br>203 |

| E.7          | FPGA to Host, UART Interface Schematic.                                           | 204        |

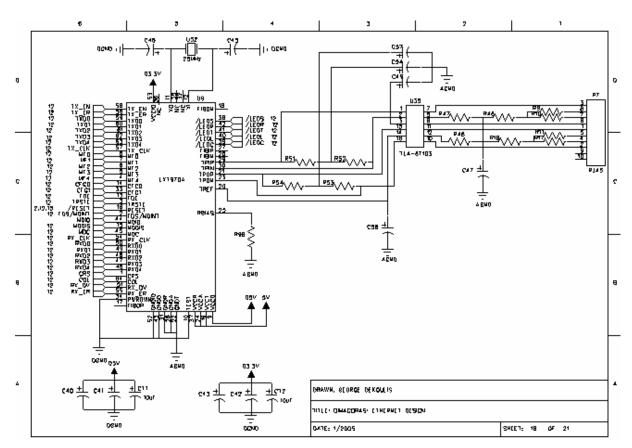

| E.8          | 10/100 Mbps Fast Ethernet Interface Schematic.                                    | 204        |

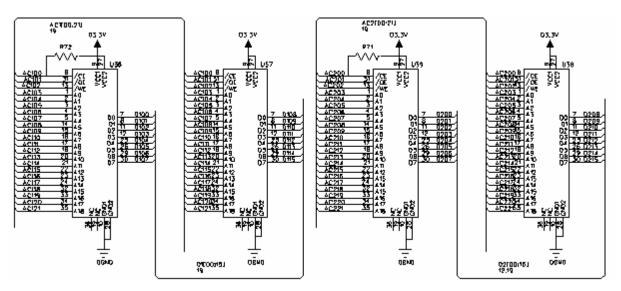

| E.9          | 16 Mbits SRAM Schematic.                                                          | 205        |

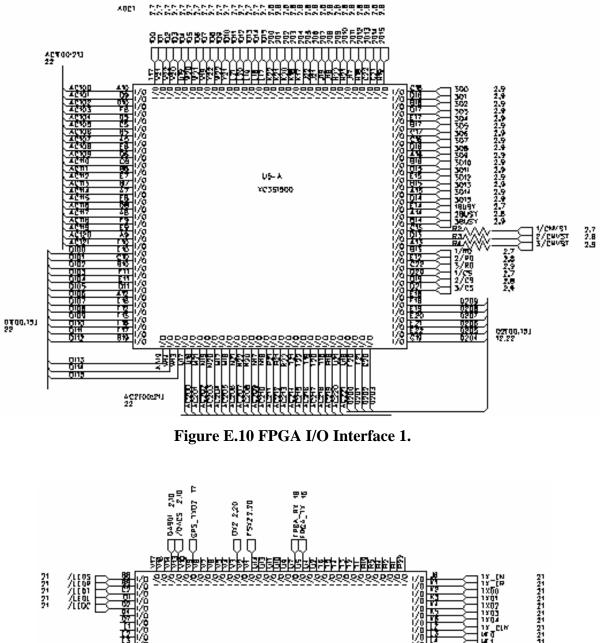

| E.10         | FPGA I/O Interface 1.                                                             | 205        |

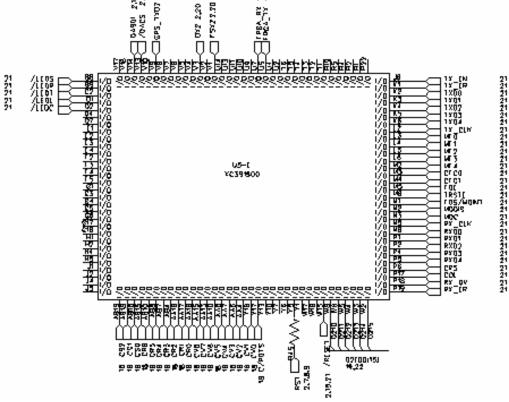

| E.11         | FPGA I/O Interface 2.                                                             | 206        |

| E.12         | FPGA Programming Interface.                                                       |            |

# List of tables

|              | IMO Vector Magnetometer Minimum Requirements.<br>IMO Scalar Magnetometer Minimum Requirements.    | 35<br>35   |

|--------------|---------------------------------------------------------------------------------------------------|------------|

| 3-1.<br>3-2. | Phase Angle and Digital Value Relationship.<br>Cross-Correlation Results Integrated Over 1 Cycle. | 60<br>63   |

|              | Soft Magnetic Alloys.<br>Maxwell Stress and Lorentz Force Results.                                | 129<br>132 |

#### Acknowledgements

I would like to thank Prof. Farideh Honary for her supervision and support.

Thank you, to Peter Chapman and the staff of the Department of Communications Systems at Lancaster University. The financial support of the Department of Communications Systems, Engineering and Physical Sciences Research Council (EPSRC) and Institute of Electrical Engineers (IEE) is cordially appreciated.

Thank you to my family and friends for their support and patience during this period.

## **Publications**

G. Dekoulis, F. Honary,"Novel Low-Power Fluxgate Sensor Using a Macroscale Optimisation Technique for Space Physics Instrumentation," Proceedings of the SPIE Smart Sensors, Actuators and MEMS III, Aerospace Applications, Vol. 6589, pp. 65890G, 2007.

G. Dekoulis, F. Honary, "Novel Sensor Design Methodology Suitable for Measurements of the Complex Solar Wind-Magnetospheric-Ionospheric System," p. 14. In Aerospace Applications of the SPIE International Symposium on Microtechnologies for the New Millenium, Maspalomas, Gran Canaria, Spain. 2nd-4th May, 2007.

G. Dekoulis, F. Honary and C. Kyriakou, "Novel Intelligent Sensor for Reconfigurable Space Physics Systems," Cy. Journ Sc. Tech., No. 2, Vol. 5, pp. 32-50, 2006.

G. Dekoulis, F. Honary, "Novel Programmable Riometer for in-depth Ionospheric and Magnetospheric ObservationS (PRIAMOS) Using Direct Sampling DSP Techniques," Proceedings of the 31st Annual European Meeting on Atmospheric Studies by Optical Methods and the 1st International Riometer Workshop, pp. 17-22, 2005.

G. Dekoulis, F. Honary and C. Kyriakou, "Unique Digital Receiver for Space Physics Instrumentation Using Reconfigurable Techniques," Cy. Journ. Sc. Tech., Vol. 4, pp. 50-61, 2005.

G. Dekoulis, F. Honary, "Novel Digital Riometer Using Direct Sampling DSP Techniques," p. 48. In 31st Annual European Meeting on Atmospheric Studies by Optical Methods and 1st International Riometer Workshop. Ambleside, UK. 22nd-28th August 2004.

M. Grill, F. Honary, E. Nielsen, T. Hagfors, G. Dekoulis, P. Chapman and H. Yamagishi, "New Imaging Riometer based on Mills Cross Technique," Proceedings of Seventh International Symposium on Communication Theory and Application (ISCTA'03), pp. 26-31, Ambleside, The Lake District, UK, July 2003.

### **Abbreviations**

ADC: Analogue-to-Digital Converter AFE: Analogue Front End AGONET: Antarctic Geospace Observatory NETwork ALU: Arithmetic Logic Unit AML: Address Matching Logic AMR: Anisotropic Magnetoresistance **API:** Applications Programmer Interface ARIES: Advanced Riometer Experiment in Scandinavia ASIC: Application Specific Integrated Circuit ATM: Asynchronous Transfer Mode **BB**: Baseband **BGS:** British Geological Survey **BJT: Bipolar Junction Transistor BM:** Butler Matrix **BPF:** Band-Pass Filter **Bps: Bits Per Second BRAM: Block RAM BW**: Bandwidth CAD: Computer Aided Design CCS: Code Composer Studio **CE:** Clock Enable CIC: Cascaded Integrator Comb CLB: Configurable Logic Block CMB: Cosmic Microwave Background CMOS: Complementary Metal-Oxide Semiconductor **CN:** Cosmic Noise CNA: Cosmic Noise Absorption COSPAR: Committee on Space Research **CPCI:** Compact PCI CPLD: Complex Programmable Logic Device **CPU: Central Processor Unit**

CRC: Cycle Redundancy Check

CSMA/CD: Carrier Sense Multiple Access with Collision Detection

DAQ: Data Acquisition

dB: Deci-Bells

DAC: Digital-to-Analogue Converter

DCE: Data Circuit-Terminating Equipment

DCM: Digital Clock Manager

DDC: Digital Down Converter

DDS: Direct Digital Synthesiser

DIGISONDE: Digital Ionosonde

DLL: Dynamic-Link Library

DMA: Direct Memory Access

DMI: Danish Meteorological Institute

DNR: Dynamic Range

DPS: Digisonde Portable Sounder

DR: Dynamic Range or Data Rate

DRC: Design Rule Check

DSK: DSP Starter Kit

DSP: Digital Signal Processor

DTE: Data Terminal Equipment

EEPROM: Electronically Erased Programmable Read Only Memory

EISCAT: European Incoherent Scatter

EMC: Electromagnetic Compatibility

EMF: Electromotive Force

EMIF: External Memory Interface

EVM: Evaluation Module

FCS: Frame Check Sequence

FDTD: Finite Difference Time Domain Method

FIT: Finite Integration Theory Method

FFT: Fast-Fourier Transform

FTP: File Transfer Protocol

FIFO: First-In First-Out

FIR: Finite Impulse Response

FPGA: Field Programmable Gate Array

FSM: Finite State Machine FWFT: First-Word Fall-Through **GMI:** Giant Magnetoimpedance GPIO: General Purpose Input/Output Port **GPRS:** General Packet Radio Services GPS: Global Positioning System GSM: Global System for Mobile Communications HF: High Frequency HF: Half-Full HPBW: Half-Power Beam Width HPI: Host Port Interface HW: Hardware I: In-Phase Component of a signal IAGA: International Association of Geomagnetism and Aeronomy IC: Integrated Circuit IF: Intermediate Frequency IFG: Inter Frame Gap IMAGE: International Monitor for Auroral Geomagnetic Effects IMF: Interplanetary Magnetic Field IMO: INTERMAGNET Magnetic Observatory INTERMAGNET: International Real-time Magnetic Observatory Network IONOSONDE: Ionospheric Sounder **IP:** Internet Protocol **IRIS:** Imaging Riometer for Ionospheric Studies ICSU: International Council of Scientific Unions **ISA:** Instruction Set Architecture ISM: Interstellar Medium **ISDN:** Integrated Services Digital Network ITU: International Telecommunication Union JTAG: Joint Test Action Group LBI: Long-Baseline Interferometry LC: Logic Cell LO: Local Oscillator LPF: Low-Pass Filter

LSB: Least Significant Bit

- LUT: Look-Up Table

- MAC: Media Access Controller

MAC: Multiply-and-Accumulate

McASP: Multi-Channel Audio Serial Port

McBSP: Multi-Channel Buffered Serial Port

MDS: Minimum Detectable Signal

MEMS : Micro-Electro-Mechanical Systems

MIPS: Mega Instructions Per Second

MMACS: Million MACs per Second

MMIC: Monolithic Microwave Integrated Circuit

MoM : Method of Moments

MPI: Max-Planck Institute

MSB: Most Significant Bit

MSPS: Mega Samples Per Second

MTBF: Mean Time Between Failure

NCD: Native Circuit Description

OIP: Output Intercept Point

**OS: Operating System**

OSI: Open Systems Interconnection Reference Model

OTR: Out-Of-Range

PAR: Place And Route

PCA: Polar Cap Absorption

PCB: Printed Circuit Board

PCI: Peripheral Components Interconnect

PCI-X: PCI Express

PENGUIn: Polar Experiment Network for Geophysical Upper-Atmosphere Investigations

PMC: PCI Mezzanine Card

PPM: Parts Per Million

PPP: Point-to-Point Protocol

PSD: Phase Sensitive Detector

PSM: Programmable Switching Matrix

Q: Quadrature Component of a signal

QDC: Quiet Day Curve

**RADAR:** Radio Direction and Ranging RAM: Random Access Memory **RF:** Radio Frequency RIOMETER: Relative Ionospheric Opacity Meter for Extra - Terrestrial Electromagnetic Radiation **ROM:** Read Only Memory **RTC: Real-Time Clock RTL:** Register Transfer Logic or Level SAMA: South Atlantic Magnetic Anomaly SAMNET: Sub-Auroral Magnetometer Network SANAE: South African National Antarctic Expedition SCAR: Scientific Committee for Antarctic Research SCNA: Sudden Cosmic Noise Absorption SCOSTEP: Committee On Solar-Terrestrial Physics SFD: Start Frame Delimiter SFDR: Spurious Free Dynamic Range SID: Sudden Ionospheric Disturbance SIM: Subscriber Identity Module SNR: Signal – to – Noise Ratio SoC: System-on-Chip SPEARS: Space Plasma Environment and Radio Science SRE: Solar Radio Emission SQUID: Superconducting Quantum Interference Device **TCP: Transmission Control Protocol TI: Texas Instruments** UART: Universal Asynchronous Receiver and Transmitter UCF: User Constraint File **UPS: Uninterrupted Power Supply USP: Unit of Space Physics** UTOPIA: Universal Test and Operations PHY Interface for ATM UV: Ultraviolet VHDL: Very High Speed Integrated Circuits Hardware Description Language V/I: Voltage-to-Current converter VLA: Very Large Array

VLBA: Very Long Baseline Array VLIW: Very Long Instruction Word WMM: World Magnetic Model

X-Bus: Expansion Bus

XDS: Extended Development System

ZBT: Zero Bus Turnaround

## Chapter 1. Introduction

The aim of the thesis is to design two novel scientific instruments for measurements of complex space physics events, namely a riometer (Relative Ionospheric Opacity Meter for Extra Terrestrial Electromagnetic Radiation) and magnetometer. The instruments have been given the acronyms Priamos (Programmable Riometer for in-depth Ionospheric and Magnetospheric Observations) and Dimagoras (Digital Magnetometer for Oracular upper-Atmospheric Studies). The novelties of the two systems are achieved by formulating and applying design methodologies resourced from the research fields of Space Physics Instrumentation, hardware, electronics, sensor systems, digital signal processing and Radio Astronomy.

A riometer measures the cosmic microwave background (CMB) absorption by the upper-atmospheric layers. Statistical analysis of the captured data yields to identification of space physics events. A riometer is categorised into passive Radio Astronomy instrumentation, since no transmitters are used. A magnetometer measures the strength of magnetic fields. Within the thesis, a magnetometer or a sensor measure the Earth's magnetic field variation. The main contribution due to the Earth's core and crustal fields is removed. The system measures the aggregate disturbed magnetic flux density due to space physics events. Both instruments provide an indirect method for studying space weather conditions.

Chapter 2 retrieves information from the six pre-mentioned research fields, with relevance to the two systems. The CMB, radio stars emissions, space physics events and noise induced from the receiver itself is the input to the riometer. Due to the low-frequency of operation, macroscale antennas are being used suitable for Radio Astronomy observations. A comparison between riometers and radio telescopes clarifies the main differences between the two classes of Radio Astronomy instruments. Existing widebeam and imaging riometer instrumentations and specifications are presented with emphasis on their scientific significance.

The Earth's core magnetic field, Earth's crustal fields and the aggregate disturbed magnetic flux density due to space physics events and any induced continental or sea fields is the input to the magnetometer. A systematic comparison between the available sensors and resulting analogue and digital magnetometers is presented. Reviewing ground-based and spaceborne magnetometers set the target specifications for the new system.

The research, so far, assisted in identifying key system parameters, setting an initial set of specifications and appreciating the scientific importance of the two systems in indirectly measuring space weather conditions. For instance, in widebeam riometer observations, the temporal resolution is inversely proportional to the bandwidth. The integration time may be reduced when the bandwidth is increased. The receiver's parameters are also affected by these variations, such as the noise figure which is proportional to the bandwidth.

It was soon realised that two digital systems architectures are required to fulfil the specifications and, to provide the expected processing power and programming flexibility. The research was directed into the available digital systems design methodologies. A comparison between the available hardware technologies is presented.

Field programmable gate arrays (FPGAs) or digital signal processors (DSPs) are commonly used for fast prototyping of algorithms and hardware designs. However, FPGAs have overcome DSPs over the recent years in terms of processing power, logic capacity, popularity amongst hardware designers and the ever increasing FPGA applications.

Recent developments in radars, remote sensing instruments, radar interferometers, sounding rockets, standard, nano- and pico- satellites and spacecrafts, robots for space exploration etc. are based on reconfigurable FPGA solutions. Specifications require future Deep Space communications developments to implement multi-protocol and reconfigurable system-on-chip (SoC) transceiving systems. Priamos and Dimagoras are implemented using reconfigurable FPGAs.

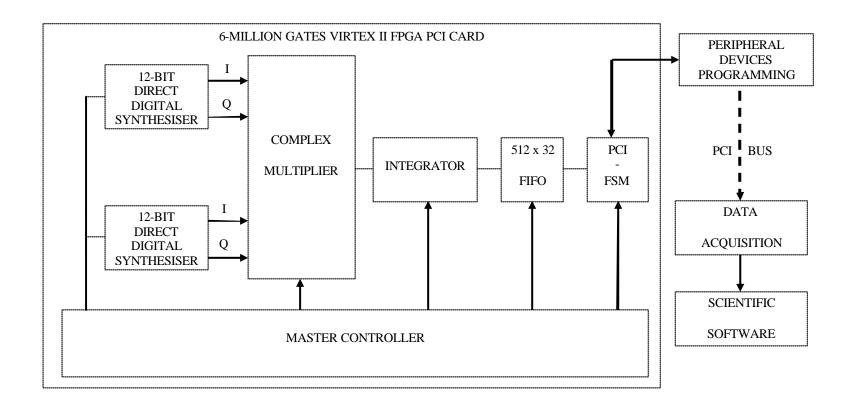

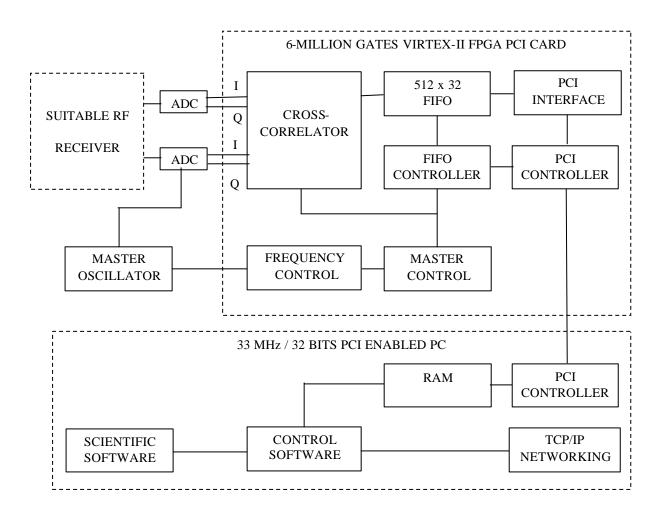

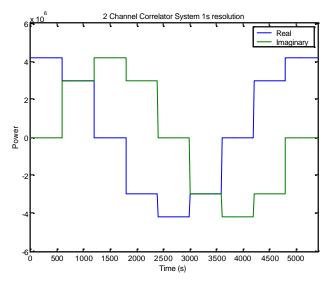

Chapter 3 evaluates the performance of the cross-correlation algorithm between nonidentical signals. The correlator is the major DSP function in every radio interferometer. Antenna-array theory is applied to derive the cross-correlation and auto-correlation functions to be modelled in hardware. A dual-channel cross-correlator system is developed and data acquisition is achieved via the 32-bits/33 MHz PCI bus. The correlator is seriatim being reused by both Priamos and Dimagoras systems.

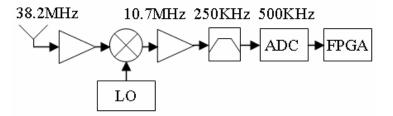

Chapter 4 describes the feasibility study, RF Receiver Unit and peripheral hardware design for Priamos. Priamos has been through many design iterations before finalising the specifications, hardware design, computer architecture and instrumentation. The final version provides a set of novel specifications and significantly improved performance over existing widebeam riometers. The RF receiver design study indicates that removing the extensively used noise balancing technique and continuously processing the input signal provides an improvement of 3 dB. The direct sampling architecture provides an improvement of 6 dB over multi-stage receivers.

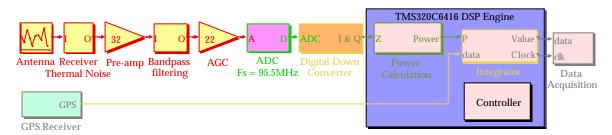

The receiver tunes to CMB emissions in the frequency range of 1 - 60 MHz. The programmable bandwidth of observation is in the range of 3 KHz – 1 MHz. The receiver has a programmable dynamic range up to 175 dB, so that saturation is avoided during strong solar radio emissions of type III and IV. The RF Receiver Unit can be installed close to the antenna for 0 dB transmission line losses. A programmable master oscillator interface generates accurate frequency sampling signals up to 250 MHz. A programmable GPS interface and instrumentation is presented for in-situ data timestamping.

Chapter 5 proceeds to the hardware design of the Priamos DSP Engine Unit. The implementation of a digital band-pass filter operating at the sampling frequency is considered first. The excessive DSP power requirements indicated that a digital down conversion stage is required before the FPGA. The DSP Engine Unit has been through three design iterations before the optimum configuration is selected and developed.

The first iteration requires a high-performance DSP evaluation kit to be interfaced by seven other prototype boards, including the RF Receiver Unit. Control over the system is limited, many programmable features are disabled and a co-processor on a

peripheral bus is still required to fully control the system. A custom DSP-based with FPGA co-processor system is considered next. The resulting hardware complexity and prototyping cost yielded to an FPGA-based solution, which is evaluated and the design is presented.

The FPGA-based Priamos DSP Engine Unit supports over 300 commands for realtime programming and reconfiguration of the system. The computer architecture is based on eight mega-functions that programme or reconfigure the FPGA, RF Receiver Unit, GPS receiver, external memory, master oscillator and glueless UART, USB 2.0 or 10/100 Mbps fast Ethernet interfaces. Priamos is the first multi-port riometer.

The system features programmable functions such as, dual-down conversion processing, auto-correlation, variable sampling frequency, universal time clock, in-situ data timestamping, storage up to 144 hours or real-time transfers. The DSP Engine Unit is independent of the antenna type being used, consisting a prototyping platform for other space physics instrumentation projects.

Chapter 6 describes the feasibility study and system analysis for Dimagoras. The analysis of existing and planned magnetometers indicated that magnetometer design is evolving rapidly. There are two general design methodologies. The first methodology involves designs where a new sensor is developed and the receiver's electronics are adjusted accordingly. The second category covers designs using an existing sensor and the receiver's architecture is adapted. The reviewed systems lack the flexibility in terms of signal processing and are tied to one sensor, operating frequency, bandwidth and dynamic range. Variable integration time instrumentations exist.

For Earth's field measurements the extra flexibility can be omitted. The study of space physics events requires flexibility in hardware and software processing. For instance, programming and expanding the dynamic range by digitally controlling the analogue circuits allows space physics events to be captured at the full-scale edges of the hardwired dynamic range that would otherwise be missed. A novel applied design methodology for engineering low-power macroscale optimised fluxgate sensors for measurements of space physics events is presented. The basic sensor saturates for an excitation current of +/- 250 mA. The optimised sensor saturates at +/- 60 mA. Power consumption is reduced by a factor of 16 and over 32 for existing spaceborne instrumentations. The low noise factor qualifies the macroscale optimised sensor for spaceborne applications. Clean room procedures and material handling are essential for maintaining both the supermalloy's and magnetic shield's high-permeability values. The sensor's sensitivity of 151 uV/nT amply covers the Earth's magnetic field variation. A tri-axial sensor is built by appropriately assembling three single-axis sensors. The sensor stipulates the DSP requirements.

Chapter 7 proceeds to the hardware design of the remaining Dimagoras system, built on the experience obtained from Priamos. The Priamos DSP Engine Unit can also be reused by modifying the FPGA's VHDL code. Dimagoras implements a novel multifrequency and multi-bandwidth scheme supporting any fluxgate sensor tuned in the frequency range of 1 KHz up to 1.5 MHz. Most of the sensors are tuned up to 100 KHz. However, oversampling increases the system's resolution and determines the noise performance and optimum frequency of operation. Dimagoras is one of the few multi-port magnetometers.

Finally, conclusions are drawn to summarise the research work and to highlight the major engineering achievements presented throughout the thesis. Future work is essential for Dimagoras in two aspects.

Other materials and sensor designs can be macroscale implemented. For instance, a new material was recently found with better specifications than supermalloy. It can be used to reduce power consumption even further using the same dimensions of the prototype cores. The optimisation technique is directly applicable in the microscale. Since nanowires exist, it is worthwhile investigating if nanotechnologies support it as well. A radiation hardened MS ASIC or FPGA solution can be devised that could qualify for Space.

Scientific software development can be expanded to include the contribution of space physics magnetometers into the World Magnetic Model for space weather short term predictions. The World Magnetic Model takes into consideration the altitude variation, so the predictive model is applicable to airborne magnetic sensors applications.

The following chapter provides information on the scientific significance of riometer and magnetometer instrumentations, as well as, digital systems design methodologies that inspired and challenged the hardware design of Priamos and Dimagoras.

### Chapter 2. Background Theory

#### 2.1 Background

A riometer is a passive radio astronomy instrument measuring the radiation intensity received from different parts of the sky and the corresponding Cosmic Noise (CN) Absorption (CNA) by the lower ionospheric layers [1].

The CMB is the major source of the sky brightness at centimetre wavelengths [2]. This corresponds to a temperature of 2.73 K and it is used to derive the brightness intensity of many other wavelengths in the near region. However, riometers operate at long radio wavelengths and up to 50 MHz. At these frequencies the brightness of the sky is more intense than expected from the CMB by itself. At 35 MHz the effective temperature is over 100,000 K.

This radiation is due to highly energetic galactic electrons radiating at these frequencies. Their spectrum is different to the black body's spectrum, safely assumed for the calculation of the different near-centimetre wavelengths cases, since the derivations do not include any radiation processes. This is because radiation used to equipoise matter at an early cosmic evolution stage, and maintained its spectrum in any seriatim expansion and cooling stages [3].

Superimposed on CN is any induced noise from the receiver itself. Including the emissions from the different radio stars at the tuned frequency, the riometer is presented with very low-power levels to be measured. Some of these radio sources have angular sizes of only one arcsec and can only be measured by radio telescopes at higher frequencies. Imaging riometers use widebeam antennas to deliberately exhibit resolution in the range of 40,000 arcsec/beam covering wider sky areas. The strongest of these sources could be detected by riometers, if more directional antenna phased-array systems are built with higher spatial resolution for resolving the acquired power measurements. Introducing higher power gain systems is not an option for the passive riometers. This applies to radio telescopes in active mode.

Radio telescopes are better operated in the frequency range 1.4 - 15 GHz, where CN radiation, atmospheric absorption in general, and ionospheric or tropospheric phase instabilities are kept to a minimum. The technology employed and the research extracted from the deployment of radio telescopes had a strong impact in the development of modern sciences.

Since 1963, Arecibo in Puerto Rico (50 MHz-10 GHz) is the world's largest singledish (305 m diameter, 50m depth) radio telescope with a 2.5 MW (BWmax = 2 MHz) planetary radar transmitter. After a short transmission (2 us - 2.1 ms), the target's size and distance is analysed by the returning echoes [4]. Long-baseline interferometry (LBI) increased resolution to x100,000 from the observer. Since 1980, the LBI Very Large Array (VLA) near Socorro, New Mexico (74 MHz-50 GHz, 0.04 arcsec maximum resolution at 43 GHz, 24 arcsec at 74 MHz) is the world's largest array of 27 25 m-diameter Y-shaped radio telescopes [5]. Since 1993, the Very Long Baseline Array (VLBA) controlled by the Array Operations Centre in Socorro, New Mexico (0.0002 arcsec maximum resolution at 43 GHz) is the world's largest astronomical instrument of ten 25 m-diameter radio telescopes [6].

In phased-array riometer systems two strong radio sources are additionally superimposed on background noise. Due to the diurnal Earth's rotation first the extragalactic source Cygnus A and, then, the supernova remnant Cassiopeia A pass through the antenna-array field-of-view. Cygnus A radio galaxy, discovered by Hey in 1946 [7], is in fact one of the strongest radio sky sources. The youngest supernova remnant in the Galaxy (300 years old) Cassiopeia A is the brightest radio source in the sky [8], but its radio emission is progressively decreasing.

CN is absorbed or attenuated as it passes through the Earth's atmosphere at certain frequencies, due to the complex solar wind-magnetospheric-ionospheric system. Highly-energetic particles with energies between 10 KeV and 100 KeV precipitate through the upper atmosphere, increasing the fractional ionospheric ionisation, especially at altitudes where electron motion is collision-dominated [9]. Absorption is a partial release of the CN energy to heat through electron collisions and is proportional to both the energy flux and observation frequency.

The influence of space weather conditions over the Earth's magnetic field can be measured by magnetometers. A basic magnetometer measures magnetic fields (e.g. a fluxgate magnetometer measures the Earth's magnetic field) or magnetic moment (e.g. a vibrating or gyratory magnetometer). The name magnetic sensor signifies sensors working on magnetic principles and in this thesis, sensors that measure the Earth's magnetic field.

Currently, the research conducted on sensors is based on miniaturisation by using new materials. Non-semiconductor sensors, such as fluxgates, induction sensors etc. are already using micro-technologies. Micro-coils and micro-relays using modern micromachining processes are described in [10]. The application of amorphous materials such as wires and tapes to sensors in general is analysed in [11].

Depending on the nature of the magnetic field under measurement, different ranges exist within the universe. Within the Space Physics context, magnetic fields of interest are the galactic magnetic field (B  $\approx 0.2$  nT), Earth's magnetic field (B  $\approx 60$  uT), white dwarf's (B  $\approx 1$  kT) and pulsar's (B  $\approx 100$  MT) [3].

A research field of interest is how the Earth's magnetic field was created, which effectively answers the question on how polarised/centralised magnetic fields can be created on other planets (e.g. Mars) to recreate Earth-like atmosphere and living conditions. Acuna [12], principal investigator of the magnetometer/electron reflectometer instrument on-board NASA's Mars Global Surveyor orbiter, verified that stronger than expected magnetic field of planetary origin exists on Mars.

Mars has no centralised field of internal origin, but must have had one in the past, when the crust acquired intense magnetisation, probably by cooling in the presence of a similar to Earth magnetic field (thermoremanent magnetisation). Planets like Jupiter, Saturn, Uranus, Neptune and Earth generate their magnetic fields by means of a dynamo made up of moving molten metal at the core. This metal is a good conductor of electricity and the rotation of the planet creates electrical currents deep within the planet that give rise to the magnetic field.

Another question that puzzled the author is what would happen in case the poles are reversed. It is well known that the Earth's magnetic field is gradually weakening ( $\approx 0.1\%$  per year), that is why the research on low frequency gravity waves, and there is a possibility in the near future of pole reversal. Of course, this requires an internal (high unlikely) or external strong threshold (e.g. a strong gravity source passing close to Earth). There are many different points of view, all supported mainly by Russian and US scientists. One recent theory about pole reversal is in [13].

The thesis is concerned with the novel hardware design of two riometer and magnetometer systems, therefore, the following sections are related to the different types of riometers and magnetometers and long-term scientific observations. The chapter concludes with the different hardware design techniques that can be used to implement the two systems.

#### 2.2 Riometry

The concept of riometry was introduced over 50 years ago [14] to collect information about the state of the lower ionosphere and to investigate phenomena, such as auroral disturbances. Thereafter, many applications and scientific literature have been derived. It is a passive radio wave experiment, since no transmitters are used. A riometer has also been used for studying the atmosphere of Mars [15].

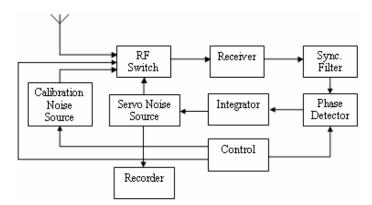

Riometers consist of low noise, sensitive receivers equipped with calibration circuits. Amplitude and, in some systems, phase, can be measured of the received sky radiation A single vertical antenna with the main lobe in the direction of local zenith can be used to form a widebeam riometer. CNA varies according to the Earth rotation, but remains constant for a repeated Local Sidereal Time. In contrast to widebeam riometers, only imaging riometers attracted detailed attention in recent years from the scientific community and funding bodies.

#### 2.2.1 Widebeam Riometers

Widebeam riometers have a single antenna above a ground plane and have been reported to operate at frequencies of 16.6 [12], 20, 20.5, 21.3 [17], 25 [17], 27.6, 29.7, 29.9, 30, 32, 32.4, 35, 38.2 and 51.4 MHz and bandwidths of 15 to 250 KHz. At frequencies below 20 MHz the cosmic radio waves are often obliterated even before reaching the ionosphere. Over 50 MHz, absorption is virtually undifferentiable from the CMB [18].

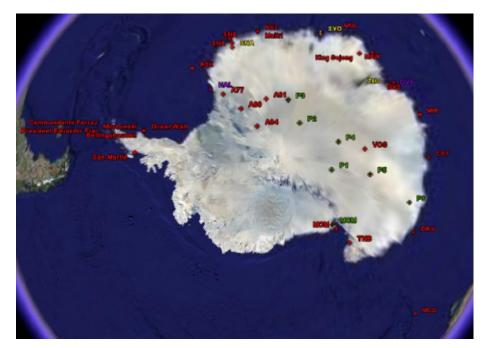

Known widebeam riometers located in the northern and southern hemispheres are red marked in Fig. 2.1 and 2.2, respectively. The antenna is usually a broadbeam design of a vertical three element Yagi, two parallel horizontal dipoles or a circularly polarised cross-dipole with a beamwidth in the region of 60°. Circularly polarised cross-dipole antennas receive both vertically and horizontally polarised transmitted radio signals. They are insensitive to plane polarisation variation due to the ionospheric Faraday rotation effect and for this reason are also used in L-band satellite systems [19].

In riometry, CN is the measurable "signal". CN has extreme random amplitude, phase and polarisation. If statistically processed, approximates Gaussian random noise. CN is subjected to both interstellar medium (ISM) and ionospheric Faraday rotation [20]. Different emissions in low frequency radio astronomy are due to the synchrotron mechanism, such as Cygnus A, quasar 3C48 etc., and linearly polarised emissions are produced [21]. OH masers from galactic star forming regions form circularly polarised microwave emissions and other interstellar maser sources often are partially linearly polarised [3]. The sources polarisation is randomised due to the magnetic fields direction variations, even within the sources, and by de-facto Faraday rotation. Circularly polarised cross-dipole antennas increase the CN power levels captured, since the random birefringence recombination at the antenna contains both partially linear (horizontal and vertical) and circular polarisations.

Figure 2.1 Northern Hemisphere Widebeam and Imaging Riometers.

Riometer networks have been used for co-ordinated experiments, e.g. auroral substorm measurements [22]. Widebeam riometer networks have measured the moving absorption [23]. The Unit of Space Physics (USP) of the North-West University in South Africa operates two La Jolla [24] parallel-dipole riometers, at 30 and 51.4 MHz in the well-resourced South African National Antrarctic Expedition (SANAE) IV base, commissioned in 1997 [25]. USP operated 3 riometers, at 20, 30 and 51.4 MHz in the SANAE III base, decommissioned at the end of 1994.

The Space and Upper Atmospheric Physics Group of the University of Maryland, US, operates five wideband riometers in Antarctica and one in Alaska, tuned to 20.5, 30, 38.2, 51.4 MHz. The integration time is 1 s. La Jolla riometers are used with two horizontal parallel-dipole antennas [26]. The Danish Meteorological Institute (DMI) operates the Greenland Riometer Array consisting of eleven widebeam riometers [27]. DMI operated a riometer in Andoya, Norway until 2002.

Figure 2.2 Southern Hemisphere Widebeam and Imaging Riometers.

The Physics of Upper Atmosphere and Environment group of the National Institute of Geophysics and Volcanology in Rome, Italy has operated two 30 and 38.2 MHz riometers in Terra Nova Bay, in the Antarctic since 1993. The integration time is 1 s. La Jolla riometers are used with two horizontal parallel-dipole antennas [28].

The Australian Antarctic Division maintains in Antarctica parallel-dipole antenna La Jolla riometers at 30 MHz with a 10 s integration time. The Swedish Institute of Space Physics in Kiruna maintains three La Jolla riometers at 30 and 38.2 MHz. ESRANGE in Sweden maintains a riometer with two beamwidths at 27.6 and 35 MHz. The NORSTAR riometer array of the Institute of Space Research at the University of Calgary consists of an array of fourteen La Jolla riometers at 30 MHz, 5 s integration time, parallel-dipole antenna and bandwidth of 150 KHz [29].

#### 2.2.2 Imaging Riometers

CNA events can be studied in a finer scale by implementing antenna phased-array imaging riometers. The antenna array elements are usually combined by a Butler Matrix [30] to form a set of regularly spaced narrow beams. CN from radio stars and galaxies is constant for a repeated Local Sidereal Time and the source power *Evel* depends on the array-beam pointing direction. Imaging riometers measure simultaneously the time-varying CNA intensities in as many directions as possible. Similar to radar and sonar measurement techniques [31], images are derived. In riometry, the images represent instantaneous absorption distributions.

Imaging riometers typically operate at 1 s time resolution and cover a sky area in the region of 250 x 250 km at ionospheric altitude of 90 km. Riometer data can be combined with data from other ground based instruments such as radars [32], magnetometers [33], ionospheric sounders (ionosondes) [34] or digisonde (digital ionosonde) portable sounder (DPS) [35] etc. or satellite remote sensing instruments [36] to study the different disturbance processes in the upper atmosphere. These processes are associated to the energetic particle precipitation during solar flares and geomagnetic storms. These are custom practices for studying space weather.

Basic imaging riometers consist of 16 antennas arranged in 4 x 4 square configurations. 16-beam riometers are green marked in Fig. 2.1 and 2.2. Most of the m are located in Antarctic. The University of Maryland, USA provided six imaging riometers for ionospheric studies (IRIS) at 38.2 MHz for each Polar Experiment Network for Geophysical Upper-Atmosphere Investigations (PENGUIn) Antarctic Geospace Observatory NETwork (AGONET). AGONET is conducted by the Scientific Committee for Antarctic Research (SCAR) and a body of the International Council of Scientific Unions (ICSU) similar to the Scientific Committee On Solar-Terrestrial Physics (SCOSTEP) since 1966 and the Committee on Space Research (COSPAR) since 1958. Each PENGUIn (n = 1 - 6) has two riometers for faster data logging, 12-bit sampling resolution and produces a complete radio image every 6 s. The Max-Planck Institute (MPI) for Aeronomy, Germany used to operate a 16-beam IRIS in Ramfjordmoen, Norway until 1995.

The South Atlantic Magnetic Anomaly (SAMA) is characterised by an Earth's minimum magnetic field intensity [37]. To study SAMA, the Southern Space Research Center (INPE) at the southern space observatory (SSO) in Brazil, in collaboration with Nagoya, Takushoku and Kyushu Universities in Japan installed a 4 x 4 beam IRIS (INPE-SSO) with 1 s time resolution and a 250 KHz bandwidth [38]. The experiment lasted until 1999.

The University of Maryland, USA installed the first IRIS system at the South Pole (SPA) (90° S, 0° E) in 1988 [39]. The system uses 64 cross-dipoles tuned to 38.2 MHz. Butler matrices form 64 in total or 49 effective beams. 64- and 49-beam riometers are yellow and purple marked in Fig. 2.1 and 2.2, respectively. The spatial resolution is about 20 km at 90 km height.

The 49 beams exiting the butler matrices connect to seven riometer receivers. Using time-division switching each riometer is fed with one of the 7 columns of 7 beams. The time resolution is 1 s. Switching is accomplished by dividing each second into 8 time slots. Each one of the 7 beams is monitored for 125 ms. The widebeam output is in the eighth slot. Each output is digitised using 8-bits in the old IRIS design, or 12-bits resolution in the newer version Data acquisition (DAQ) software stores data for scientific analysis.

The Space Plasma Environment and Radio Science (SPEARS) Group of Lancaster University, has been operating IRIS at Kilpisjarvi (KIL), Finland since 1994 [40-41]. The antenna array consists of 64 antennas. 49 narrow effective beams are produced of angular resolution of 12° half-power beamwidth. Other IRIS systems are installed at DVS, HAL, STF, IQA, LYR, NAL, ZHS, SNA, TJO, SYO, HUS and DMH stations, operating at 30 or 38.2 MHz.

The world's largest field-array IRIS system is operated in the Poker Flat (PKR) Research Range in Alaska. A 256 beam cross-dipole antenna array arranged in 16 x 16 square is used to form 208 effective power beams within the 70° zenith angle [42-43]. The time resolution is 1 s. The viewing area is 400 x 400 km<sup>2</sup> at 90 km. The spatial resolution is approximately 11 km around zenith.

#### 2.2.3 Solar Wind-Magnetospheric-Ionospheric Riometer Events

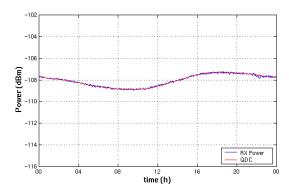

DAQ results are statistically processed to produce experimental quiet day curves (QDCs). Theoretical QDCs can be produced if a radio sky map is available at the frequency of interest. Knowledge of the antenna's radiation pattern and the system's geographical (or Global Positioning System (GPS)) location are also required. The Lancaster University Riosim Simulator can be used for calculating theoretical QDCs. CNA is the difference between the theoretical and experimental QDCs. CNA is visualised by images and keograms in different coordinate systems. Polar cap absorption (PCA), sudden ionospheric disturbances (SIDs), auroral absorption, solar radio emissions (SREs), scintillation and lightning leave their signature on QDCs. The QDC shows the CN level on a day without absorption, SREs, PCA, SIDs etc.

Figure 2.3 Experimental and Theoretical QDCs.