# Analysing and Reducing Costs of Deep Learning Compiler Auto-tuning

Damian Borowiec, BSc (Hons)

School of Computing and Communications

Lancaster University

This thesis is submitted for the degree of  $Doctor \ of \ Philosophy$

March, 2023

This page is left intentionally blank

I dedicate this thesis to my mother Celina.

This page is left intentionally blank

#### Analysing and Reducing Costs of Deep Learning Compiler Auto-tuning

School of Computing and Communications, Lancaster University This thesis is submitted for the degree of *Doctor of Philosophy*. March, 2023

### Abstract

Deep Learning (DL) is significantly impacting many industries, including automotive, retail and medicine, enabling autonomous driving, recommender systems and genomics modelling, amongst other applications. At the same time, demand for complex and fast DL models is continually growing. The most capable models tend to exhibit highest operational costs, primarily due to their large computational resource footprint and inefficient utilisation of computational resources employed by DL systems. In an attempt to tackle these problems, DL compilers and auto-tuners emerged, automating the traditionally manual task of DL model performance optimisation. While auto-tuning improves model inference speed, it is a costly process, which limits its wider adoption within DL deployment pipelines.

The high operational costs associated with DL auto-tuning have multiple causes. During operation, DL auto-tuners explore large search spaces consisting of billions of tensor programs, to propose potential candidates that improve DL model inference latency. Subsequently, DL auto-tuners measure candidate performance in isolation on the target-device, which constitutes the majority of auto-tuning compute-time. Suboptimal candidate proposals, combined with their serial measurement in an isolated target-device lead to prolonged optimisation time and reduced resource availability, ultimately reducing cost-efficiency of the process.

In this thesis, we investigate the reasons behind prolonged DL auto-tuning and quantify their impact on the optimisation costs, revealing directions for improved DL auto-tuner design. Based on these insights, we propose two complementary systems: Trimmer and DOPpler. Trimmer improves tensor program search efficacy by filtering out poorly performing candidates, and controls end-to-end auto-tuning using cost objectives, monitoring optimisation cost. Simultaneously, DOPpler breaks long-held assumptions about the serial candidate measurements by successfully parallelising them intra-device, with minimal penalty to optimisation quality. Through extensive experimental evaluation of both systems, we demonstrate that they significantly improve cost-efficiency of autotuning (up to 50.5%) across a plethora of tensor operators, DL models, auto-tuners and target-devices.

### Acknowledgements

I would like to thank all those who supported me during my PhD journey, both academically and otherwise. I direct my first and foremost gratitude to my academic supervisors, Dr. Peter Garraghan and Professor Richard R. Harper for their endless help, academic and personal support as well as numerous opportunities they have offered me over the course of the past four years.

I would like to thank Peter for his continual reassurance in times where I doubted myself, and for his dedication and effort to help me understand that there are always options out there and I just need to step back and think. I look back fondly at the numerous late night calls, publication writing sessions and countless feedback on the drafts of this research work. Beyond research, I am grateful to Peter for his continual push towards improvements in my presentation, public speaking, teaching and leadership skills, which all have greatly flourished thanks to his guidance.

I am thankful to Richard for his guidance and supervision, on many occasions when I needed it the most. I would like to thank him for the opportunity of being part of the Material Social Futures Centre for Doctoral Training, which had an inestimable impact on my personal growth as a researcher, as well as many career, networking and academic opportunities he has offered me throughout my PhD journey. If I was to pick a single thing I learned from Richard, it would be to remain specific yet keep my mind open to the broader impact of my work.

For the mutual exchange of ideas and comradery I would like to thank all current and former members of the Experimental Distributed Systems Lab. I send my special thanks to Ging Fung Yeung for his ongoing guidance, close collaboration on various projects and publications as well as moral support. Thank you to Dominic Lindsay, William Hackett, Lewis Birch, Stefan Trawicki, James Bulman and Matthew Hodkin for their efforts in the ongoing battle with the compute cluster downstairs and lab equipment as well as many fruitful conversations. I would like to thank Petter Terenius for our many collaborative and casual conversations throughout the years, and I truly believe your work is going to revolutionise the way we think about energy in datacentres. Thank you to Marta Adamska, Daria Smirnova, Sukhpal Singh Gill, Weija Li and John Hutchinson for making the PhD experience a more enriching one.

I would like to thank all current and former members of the Material Social Futures Centre for Doctoral Training for in-depth discussions on academic topics seemingly far outside my realm of research, yet in the end extremely eye-opening and useful especially Christina Bremer, Ben Wood, Ariel Bernier and Sophie Au-yong. Thank you to all supervisors, speakers and the managerial board for sharing their multi-disciplinary knowledge in such an approachable way. Also, I would like to thank the MSF Centre for Doctoral Training and the Leverhulme Trust for providing me with the PhD studentship.

Thank you to Dr. Andrew Scott for an excellent supervision of my BSc FYP which has ultimately led to my interest in systems research and this thesis. I am grateful to my colleagues for their support and collaboration during my internships at Microsoft Research Cambridge and Huawei Research and Development Edinburgh. Both experiences have provided me with necessary industry and academic knowledge and confidence to complete this work, growing as a researcher and systems engineer.

Thank you to my friends - especially Eleanor Davies for keeping me sane. I want to thank my close family - brother Krzysztof, niece and nephews for their love and belief in my ability to complete my PhD, and especially my mother Celina - without whom I would not have been able to achieve this, and who has been there whenever I needed her. *Dziękuję za wszystko Mamo*. Finally, I would like to thank my partner, Niah who has accompanied me in the many ups and downs of my work and life and continues to help me see the bright side of things - with loving support.

### Declaration

I declare that the work presented in this thesis is, to the best of my knowledge and belief, original and my own work. The material has not been submitted, either in whole or in part, for a degree at this, or any other university. This thesis does not exceed the maximum permitted word length of 80,000 words, including footnotes, but excluding the bibliography, appendices and the front matter. A rough estimate of the word count is: 53029

> Damian Borowiec March, 2023

This page is left intentionally blank

### List of Publications

• Borowiec, D., Yeung, G., Friday, A., Harper, R., Garraghan, P., 2023. DOPpler: Parallel Tuning for Deep Learning Tensor Programs. In: IEEE Transactions on Parallel and Distributed Systems (TPDS), Vol 34, No. 7, pp. 2208-2220.

I designed, implemented and evaluated DOPpler. Ging Fung Yeung contributed towards the design of the alternative DOPpler policy (RLEARN), and provided guidance during design of the Calibrator module. Peter Garraghan contributed towards system design and paper writing. Adrian Friday and Richard Harper provided feedback, helped with revisions and improved the paper.

The analysis of naïve parallel measurements during DL auto-tuning form the basis of Chapter 5 whilst Chapter 6 presents the design and evaluation of DOPpler.

• Borowiec, D., Yeung, G., Friday, A., Harper, R., Garraghan, P., 2022. Trimmer: Cost-Efficient Deep Learning Auto-tuning for Cloud Datacenters. In: IEEE International Conference on Cloud Computing (CLOUD 22), pp. 374-384.

I designed, implemented and evaluated Trimmer. The cold-candidate filtering model is a joint contribution with Ging Fung Yeung. Peter Garraghan contributed towards system design and paper writing. The paper was reviewed and improved by Adrian Friday and Richard Harper.

The analysis of DL optimisation method costs presented within the paper, forms the basis of Chapter 3 while the design and experimental evaluation of Trimmer form the basis of Chapter 4. • Borowiec, D., Harper, R., Garraghan, P., 2022. Environmental Consequence of Deep Learning. In: ITNOW, Vol. 63, No. 4, pp. 10-11.

I wrote the paper. Richard Harper and Peter Garraghan contributed towards initial idea discussions, provided feedback and helped revise the paper.

This paper contributes to broader DL costs discussions in Chapters 1 and 7.

Yeung, G. Borowiec, D., Yang, R., Friday, A., Harper, R. and Garraghan, P., 2022. Horus: Interference-Aware and Prediction-Based Scheduling in Deep Learning Systems. In: IEEE Transactions on Parallel and Distributed Systems (TPDS), Vol. 33, No. 1, pp. 88-100.

Ging Fung Yeung designed Horus and its evaluation methodology. I contributed towards the implementation of the profiling engine and evaluation scripts, implemented the Open Neural Network Exchange (ONNX) analyser, performed model co-location experiments and collected the associated data as well as helped with paper writing. Renyu Yang, Adrian Friday, Richard Harper and Peter Garraghan helped with paper writing, design discussions and revisions of the work.

The ONNX analyser was partially re-used to characterise models used across Chapters 3, 4, 5 and 6, while the profiling engine was further extended to monitor compute platforms during evaluation experiments (Trimmer and DOPpler). Moreover, this paper explores the problem of interference when co-locating DL workloads, which feeds into the investigation performed as part of Chapter 5.

### Contents

| $\mathbf{C}$    | onter             | $\mathbf{nts}$ |                                                   | -   | xiii |

|-----------------|-------------------|----------------|---------------------------------------------------|-----|------|

| List of Figures |                   |                |                                                   | :   | xxi  |

| $\mathbf{Li}$   | List of Tables xx |                |                                                   |     | xix  |

| $\mathbf{Li}$   | ist of            | Listin         | ıgs                                               | x   | xxi  |

| $\mathbf{Li}$   | ist of            | Abbr           | eviations                                         | XXX | viii |

| 1               | Intr              | roduct         | ion                                               |     | 1    |

|                 | 1.1               | Motiv          | ration                                            |     | 1    |

|                 |                   | 1.1.1          | High Operational Costs in Deep Learning           |     | 2    |

|                 |                   | 1.1.2          | Optimising Model Inference Performance            |     | 3    |

|                 |                   | 1.1.3          | Deep Learning Compilers                           |     | 3    |

|                 |                   | 1.1.4          | Deep Learning Compiler Auto-tuning                |     | 4    |

|                 |                   | 1.1.5          | Costs of Optimising Deep Learning Model Inference |     | 5    |

|                 | 1.2               | Recen          | t Challenges within DL Auto-tuning                |     | 6    |

|                 |                   | 1.2.1          | Serial Candidate Latency Measurements             |     | 6    |

|                 |                   | 1.2.2          | Sequential End-to-end Auto-tuning                 |     | 6    |

|                 |                   | 1.2.3          | Unfiltered Candidate Measurements                 |     | 7    |

|                 | 1.3               | Objec          | tive, Hypothesis and Research Questions           |     | 8    |

|          | 1.4 | Broad  | er Research Context                           | 10 |

|----------|-----|--------|-----------------------------------------------|----|

|          | 1.5 | Core l | Research Contributions                        | 11 |

|          | 1.6 | Thesis | s Structure                                   | 12 |

| <b>2</b> | Bac | kgrou  | nd and Related Work                           | 15 |

|          | 2.1 | Machi  | ine Learning (ML)                             | 16 |

|          |     | 2.1.1  | Model Training                                | 17 |

|          |     | 2.1.2  | Machine Learning Characterisation             | 18 |

|          | 2.2 | Deep   | Learning                                      | 21 |

|          |     | 2.2.1  | Artificial Neural Networks                    | 22 |

|          |     | 2.2.2  | Deep Neural Networks and Their Layers         | 27 |

|          |     | 2.2.3  | Systems for DNN Computation                   | 31 |

|          | 2.3 | Deep   | Learning Systems & Computation                | 32 |

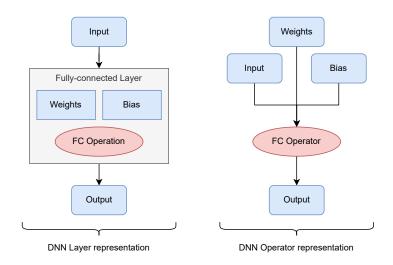

|          |     | 2.3.1  | Tensors and Tensor Operators                  | 32 |

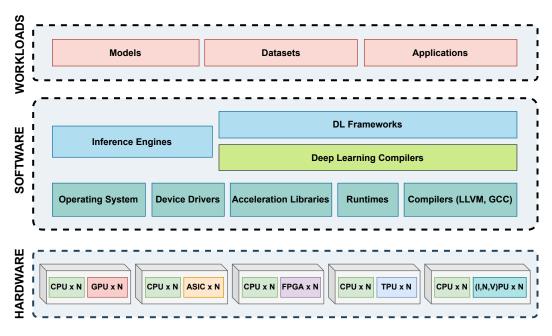

|          |     | 2.3.2  | Deep Learning Systems                         | 35 |

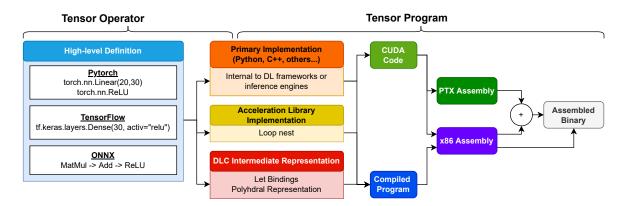

|          |     | 2.3.3  | Tensor Programs and Their Execution           | 43 |

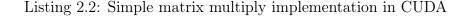

|          |     | 2.3.4  | Deep Learning Model Life Cycle                | 49 |

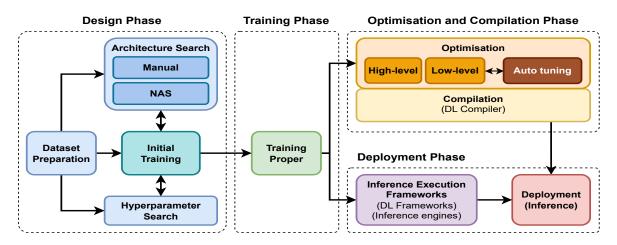

|          |     | 2.3.5  | Machine Learning as a Service (MLaaS)         | 52 |

|          | 2.4 | Chara  | cterising Deep Learning Systems               | 53 |

|          |     | 2.4.1  | Characterising Models                         | 53 |

|          |     | 2.4.2  | Characterising Hardware and its Performance   | 56 |

|          |     | 2.4.3  | Characterising Model Execution and Efficiency | 60 |

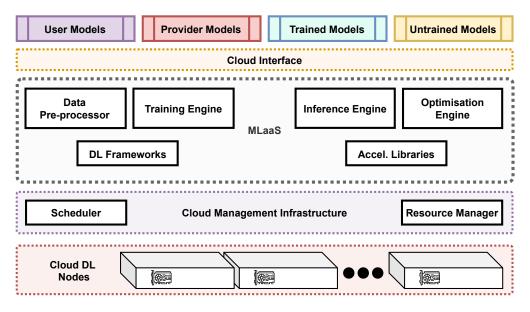

|          | 2.5 | Deep   | Learning Compilers                            | 63 |

|          |     | 2.5.1  | Existing Deep Learning Compilers              | 65 |

|          |     | 2.5.2  | Deep Learning Compiler Frontend               | 68 |

|          |     | 2.5.3  | High-level Optimisations                      | 69 |

|          |     | 2.5.4  | Deep Learning Compiler Backend                | 73 |

|          |     | 2.5.5  | Low-level Optimisations                       | 76 |

|   |        | 2.5.6  | Code Generation                        | 83  |

|---|--------|--------|----------------------------------------|-----|

|   | 2.6    | Deep   | Learning Auto-Tuning & Autoscheduling  | 84  |

|   |        | 2.6.1  | Overview                               | 84  |

|   |        | 2.6.2  | DL Auto-tuner Operation and Components | 86  |

|   |        | 2.6.3  | DL Auto-tuner Types                    | 92  |

|   | 2.7    | Chapt  | er Summary                             | 94  |

| 3 | $\cos$ | t of D | eep Learning Optimisation              | 97  |

|   | 3.1    | Study  | Setup                                  | 99  |

|   |        | 3.1.1  | DL models                              | 99  |

|   |        | 3.1.2  | Hardware Platforms                     | 100 |

|   |        | 3.1.3  | Software                               | 100 |

|   |        | 3.1.4  | High-level Optimisations               | 101 |

|   |        | 3.1.5  | Low-level Optimisations - Auto-tuning  | 101 |

|   |        | 3.1.6  | Collected Metrics                      | 102 |

|   | 3.2    | High-l | evel Transformations and Optimisations | 102 |

|   |        | 3.2.1  | The choice of a DL Framework           | 102 |

|   |        | 3.2.2  | Impact of the Hardware Platform        | 104 |

|   |        | 3.2.3  | Impact of High-level Optimisations     | 105 |

|   | 3.3    | Tenso  | r Operator Auto-tuning                 | 107 |

|   |        | 3.3.1  | Performance and Runtime Energy Costs   | 108 |

|   |        | 3.3.2  | Costs Across Different Auto-tuners     | 109 |

|   | 3.4    | Source | es of Inefficiencies in DL Auto-tuning | 110 |

|   |        | 3.4.1  | Erroneous Candidate Schedules          | 111 |

|   |        | 3.4.2  | Identifying Cold Candidates            | 113 |

|   |        | 3.4.3  | Impact of cold candidates              | 115 |

|   |        | 3.4.4  | Converging Onto Hot Candidates         | 115 |

|   | 3.5    | Findir | ngs and Design Directions              | 116 |

#### Contents

| 4        | Trii | nmer:   | Cost-Efficient DL Auto-tuning                      | 119 |

|----------|------|---------|----------------------------------------------------|-----|

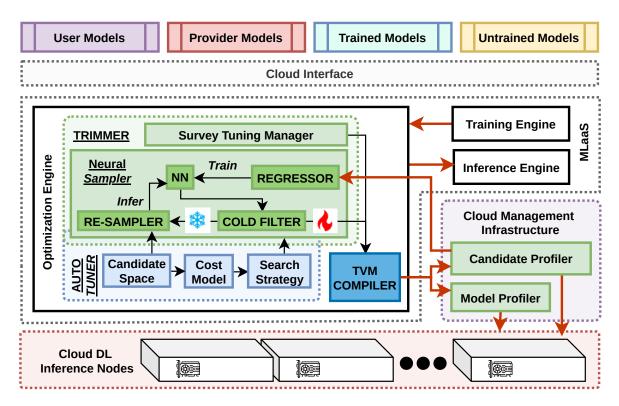

|          | 4.1  | Syster  | n Design and Implementation                        | 120 |

|          |      | 4.1.1   | Trimmer's Objective                                | 120 |

|          |      | 4.1.2   | Cold Candidate Filtering                           | 121 |

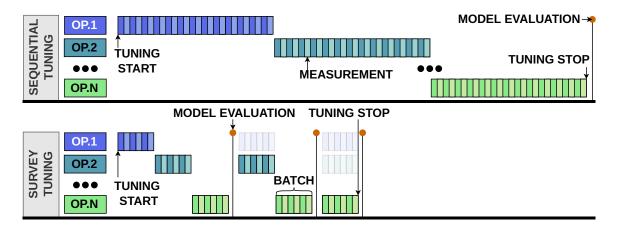

|          |      | 4.1.3   | Survey Tuning                                      | 127 |

|          | 4.2  | Exper   | iment Setup                                        | 133 |

|          |      | 4.2.1   | Hardware, Software and Middleware                  | 133 |

|          |      | 4.2.2   | Auto-tuners                                        | 133 |

|          |      | 4.2.3   | Workloads                                          | 134 |

|          |      | 4.2.4   | Collected Metrics                                  | 134 |

|          |      | 4.2.5   | Experiment Scenarios                               | 135 |

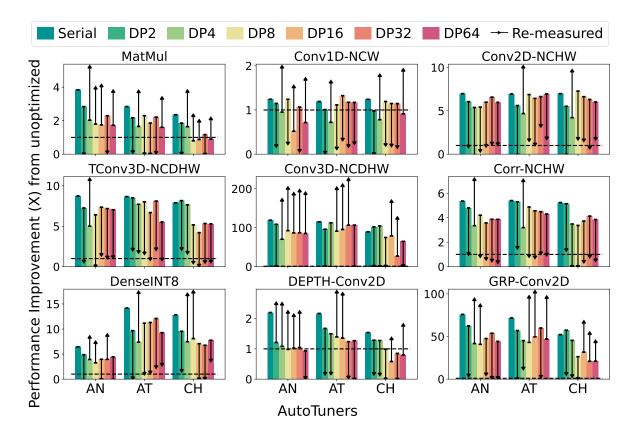

|          | 4.3  | Evalua  | ation Results                                      | 135 |

|          |      | 4.3.1   | Single Platform, Sequential Auto-tuning            | 135 |

|          |      | 4.3.2   | Cloud Clusters                                     | 139 |

|          | 4.4  | Discus  | ssion and Limitations                              | 141 |

|          |      | 4.4.1   | Auto-tuner Compatibility                           | 141 |

|          |      | 4.4.2   | Target-device Compatibility                        | 142 |

|          |      | 4.4.3   | FC NN Model Training                               | 142 |

|          |      | 4.4.4   | Workloads compatibility                            | 143 |

|          |      | 4.4.5   | Scalability                                        | 143 |

| <b>5</b> | AN   | Vaïvely | y-parallel Approach to Reduce DL Auto-tuning Costs | 145 |

|          | 5.1  | Overv   | iew                                                | 145 |

|          | 5.2  | Levera  | aging Parallelism During Measurements              | 148 |

|          |      | 5.2.1   | Existing Inter-device Parallel Measurements        | 148 |

|          |      | 5.2.2   | Naïve Intra-device Parallel Measurements           | 149 |

|          | 5.3  | Exper   | iment Setup                                        | 150 |

|          |      | 5.3.1   | Hardware Platforms                                 | 150 |

|   |     | 5.3.2  | Software, Middleware and Auto-tuners                   | 151 |

|---|-----|--------|--------------------------------------------------------|-----|

|   |     | 5.3.3  | Workloads                                              | 152 |

|   |     | 5.3.4  | Collected Metrics                                      | 153 |

|   |     | 5.3.5  | Experiments                                            | 153 |

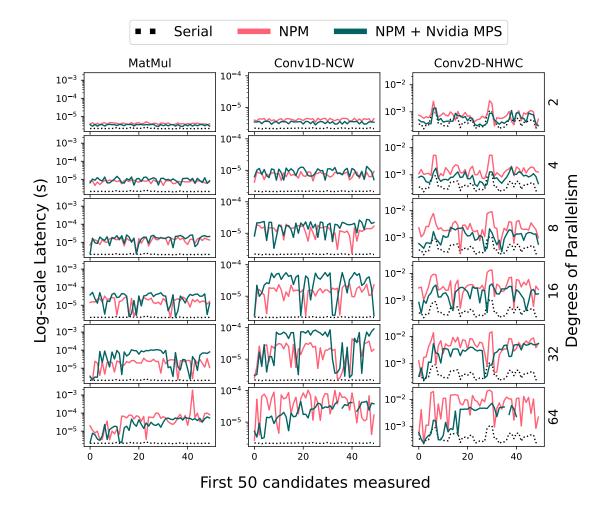

|   | 5.4 | Exper  | iment Results                                          | 154 |

|   |     | 5.4.1  | Auto-tuning time cost                                  | 155 |

|   |     | 5.4.2  | Quality of Candidate Measurements                      | 160 |

|   | 5.5 | Findir | ngs and Design Directions                              | 166 |

| 6 | DO  | Ppler: | Parallel Measurement Infrastructure for DL Auto-tuning | 169 |

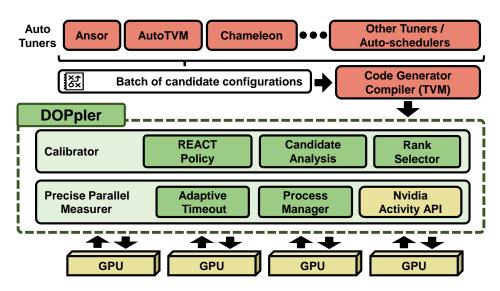

|   | 6.1 | System | n Design and Implementation                            | 170 |

|   |     | 6.1.1  | DOPpler's Objectives                                   | 171 |

|   |     | 6.1.2  | Precise Parallel Measurer                              | 172 |

|   |     | 6.1.3  | Calibrator                                             | 176 |

|   | 6.2 | Exper  | iment Setup                                            | 183 |

|   |     | 6.2.1  | Hardware, Software, Middleware and Auto-tuners         | 183 |

|   |     | 6.2.2  | Workloads                                              | 184 |

|   |     | 6.2.3  | Performed Experiments                                  | 185 |

|   |     | 6.2.4  | DOPpler's Hyperparameters and Sensitivity Analysis     | 186 |

|   |     | 6.2.5  | Collected Metrics                                      | 187 |

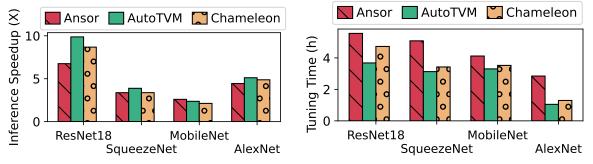

|   | 6.3 | Evalua | ation Results                                          | 188 |

|   |     | 6.3.1  | Auto-tuning Time Cost - Single Target-device           | 188 |

|   |     | 6.3.2  | Achieved Execution Latency - Single Target-device      | 190 |

|   |     | 6.3.3  | End-to-end DL Model Auto-tuning                        | 191 |

|   |     | 6.3.4  | Leveraging Multiple Target-devices                     | 192 |

|   |     | 6.3.5  | Auto-tuning Large Tensor Operators                     | 194 |

|   |     | 6.3.6  | Number of Performed Measurements and Repeats           | 196 |

|   |     | 6.3.7  | $d_p$ and Dynamic Timeout                              | 198 |

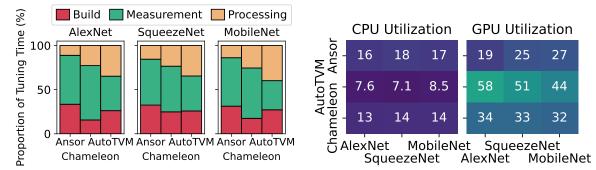

|   |     | 6.3.8   | Platform Utilisation                                    | 199 |

|---|-----|---------|---------------------------------------------------------|-----|

|   |     | 6.3.9   | Alternative Calibrator Policies                         | 200 |

|   |     | 6.3.10  | Hyperparameter Sensitivity Analysis                     | 201 |

|   | 6.4 | Discus  | sion and Limitations                                    | 204 |

|   |     | 6.4.1   | Auto-tuner Compatibility                                | 204 |

|   |     | 6.4.2   | Target-device Compatibility                             | 204 |

|   |     | 6.4.3   | Workloads compatibility                                 | 205 |

|   |     | 6.4.4   | Cost vs. Quality                                        | 206 |

|   |     | 6.4.5   | Scalability                                             | 206 |

| 7 | Con | clusio  | n                                                       | 207 |

|   | 7.1 | Resear  | ch Problem Summary                                      | 207 |

|   | 7.2 | Summ    | ary of Contributions                                    | 208 |

|   |     | 7.2.1   | Analysis of DL Optimisation Costs and Inefficiencies    | 209 |

|   |     | 7.2.2   | Cost-efficient DL Auto-tuning Filtering and Meta-tuning | 210 |

|   |     | 7.2.3   | Analysis of Parallel Candidate Measurements             | 211 |

|   |     | 7.2.4   | Parallel Intra-device Measurement Infrastructure        | 211 |

|   | 7.3 | Review  | v of Research Questions                                 | 212 |

|   | 7.4 | Self-an | alysis of Research Costs                                | 216 |

|   |     | 7.4.1   | Assumptions and Context                                 | 217 |

|   |     | 7.4.2   | Experimental Research Costs                             | 221 |

|   |     | 7.4.3   | Observations                                            | 223 |

|   |     | 7.4.4   | Broader Research Context                                | 224 |

|   | 7.5 | Future  | e Work                                                  | 224 |

|   |     | 7.5.1   | Alternative Candidate Filters                           | 225 |

|   |     | 7.5.2   | Polymorphic Auto-tuning                                 | 225 |

|   |     | 7.5.3   | Alternative Calibration Policies                        | 226 |

|   |     | 7.5.4   | Auto-tuning as a Service                                | 226 |

|              | 7.6                                                        | Recommendations for Stakeholders                                                                                                                                            | 2                                                             | 228                                                                                                                                                    |

|--------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                                            | 7.6.1 DL Engineers                                                                                                                                                          | 2                                                             | 228                                                                                                                                                    |

|              |                                                            | 7.6.2 MLaaS Cloud Providers                                                                                                                                                 | 2                                                             | 228                                                                                                                                                    |

|              |                                                            | 7.6.3 DL Compiler Engineers                                                                                                                                                 | 2                                                             | 229                                                                                                                                                    |

| Re           | efere                                                      | ences                                                                                                                                                                       | 2                                                             | 231                                                                                                                                                    |

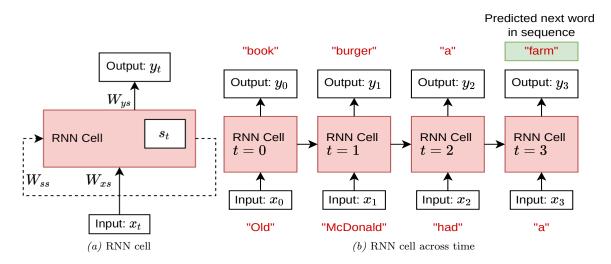

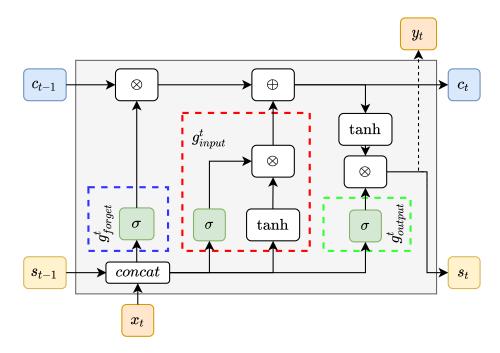

| $\mathbf{A}$ | Rec                                                        | current Cell Layers and LSTMs                                                                                                                                               | 2                                                             | 291                                                                                                                                                    |

|              | A.1                                                        | Recurrent Cell Layers                                                                                                                                                       | 2                                                             | 291                                                                                                                                                    |

|              | A.2                                                        | 2 Long Short Term Memory Layers                                                                                                                                             | 2                                                             | 293                                                                                                                                                    |

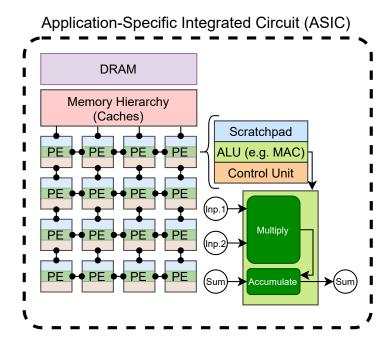

| В            | Spa                                                        | atial Dataflow Processors (SDP)                                                                                                                                             | 2                                                             | 295                                                                                                                                                    |

|              | B.1                                                        | Application-specific Integrated Circuits (ASIC)                                                                                                                             | 2                                                             | 296                                                                                                                                                    |

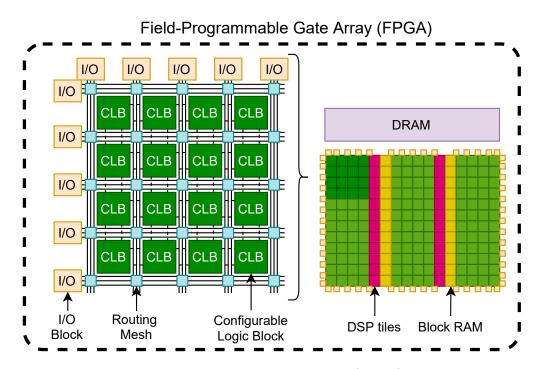

|              | B.2                                                        | 2 Field-programmable Gate Arrays (FPGA)                                                                                                                                     | 2                                                             | 297                                                                                                                                                    |

|              |                                                            |                                                                                                                                                                             |                                                               |                                                                                                                                                        |

| С            | Det                                                        | etails of standalone tensor operators used in experiment                                                                                                                    | ation 2                                                       | 299                                                                                                                                                    |

| C<br>D       |                                                            | etails of standalone tensor operators used in experiments                                                                                                                   |                                                               | 299<br>301                                                                                                                                             |

| _            |                                                            | nodel architecture details                                                                                                                                                  | 3                                                             |                                                                                                                                                        |

| _            | $\mathbf{DL}$                                              | L model architecture details                                                                                                                                                | <b>3</b><br>3                                                 | <b>6</b> 01                                                                                                                                            |

| _            | <b>DL</b><br>D.1                                           | <b>2 model architecture details</b><br>1 AlexNet                                                                                                                            | <b>3</b><br>3<br>3                                            | <b>801</b><br>301                                                                                                                                      |

| _            | <b>DL</b><br>D.1<br>D.2<br>D.3                             | L model architecture details         L AlexNet         2 SqueezeNet                                                                                                         | <b>3</b><br>3<br>3                                            | <b>301</b><br>301<br>302                                                                                                                               |

| _            | <b>DL</b><br>D.1<br>D.2<br>D.3                             | L       model architecture details         L       AlexNet         2       SqueezeNet         3       MobileNetV1         4       MobileNetV2                               | <b>3</b><br>• • • • • • • • 3<br>• • • • • • • • 3<br>• • • • | <b>301</b><br>301<br>302<br>303                                                                                                                        |

| _            | <b>DL</b><br>D.1<br>D.2<br>D.3<br>D.4                      | L       model architecture details         L       AlexNet         2       SqueezeNet         3       MobileNetV1         4       MobileNetV2         5       ConvNeXt      | <b>3</b> 3 3                                                  | <b>301</b><br>302<br>303<br>305                                                                                                                        |

| _            | <b>DL</b><br>D.1<br>D.2<br>D.3<br>D.4<br>D.5<br>D.6        | L       model architecture details         L       AlexNet         2       SqueezeNet         3       MobileNetV1         4       MobileNetV2         5       ConvNeXt      | <b>3</b>                                                      | <b>301</b><br>302<br>303<br>305<br>307                                                                                                                 |

| _            | <b>DL</b><br>D.1<br>D.2<br>D.3<br>D.4<br>D.5<br>D.6        | A model architecture details         AlexNet         2 SqueezeNet         3 MobileNetV1         4 MobileNetV2         5 ConvNeXt         6 DenseNet-121         7 ResNet-18 | <b>3</b>                                                      | <b>301</b><br>302<br>303<br>305<br>307<br>309                                                                                                          |

| _            | DL<br>D.1<br>D.2<br>D.3<br>D.4<br>D.5<br>D.6<br>D.7<br>D.8 | A model architecture details         AlexNet         2 SqueezeNet         3 MobileNetV1         4 MobileNetV2         5 ConvNeXt         5 DenseNet-121         7 ResNet-18 | <b>3</b>                                                      | <ul> <li><b>301</b></li> <li><b>302</b></li> <li><b>303</b></li> <li><b>305</b></li> <li><b>307</b></li> <li><b>309</b></li> <li><b>311</b></li> </ul> |

| $\mathbf{F}$ | Aut  | o-tuner hyperparameter details                                     | 316 |

|--------------|------|--------------------------------------------------------------------|-----|

| $\mathbf{G}$ | Trir | nmer FC ANN Model Definition                                       | 319 |

| н            | Naï  | ve Parallel Auto-tuning - Additional Results                       | 320 |

|              | H.1  | Measurement Inaccuracy during NPM/MPS                              | 320 |

|              | H.2  | Measurement Outcomes During NPM Auto-tuning                        | 323 |

| Ι            | DO   | Ppler - Additional Results                                         | 328 |

|              | I.1  | $d_p$ Over Time Across Tensor Operators and Tensor Programs        | 328 |

|              | I.2  | Timeout Setpoint Over Time Across Platforms and Tensor Operators . | 332 |

|              | I.3  | Low-level View of the Candidate Measurement Procedure              | 335 |

| Gl           | ossa | ry                                                                 | 337 |

# List of Figures

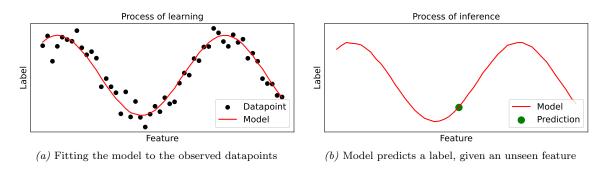

| 2.1 | Learn   | ing and inference phases of Machine Learning       | 16 |

|-----|---------|----------------------------------------------------|----|

|     | a       | Fitting the model to the observed datapoints       | 16 |

|     | b       | Model predicts a label, given an unseen feature    | 16 |

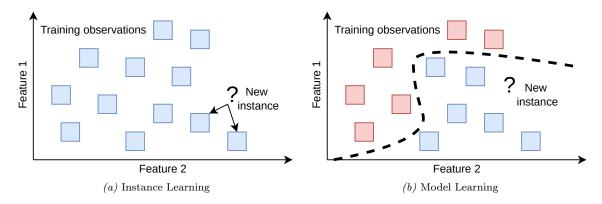

| 2.2 | Differe | ences between Instance Learning and Model Learning | 18 |

|     | a       | Instance Learning                                  | 18 |

|     | b       | Model Learning                                     | 18 |

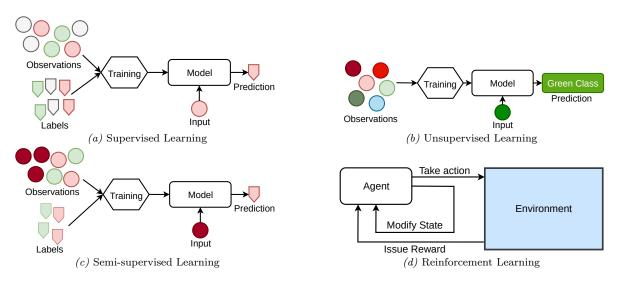

| 2.3 | Differe | ent ML paradigms                                   | 19 |

|     | a       | Supervised Learning                                | 19 |

|     | b       | Unsupervised Learning                              | 19 |

|     | С       | Semi-supervised Learning                           | 19 |

|     | d       | Reinforcement Learning                             | 19 |

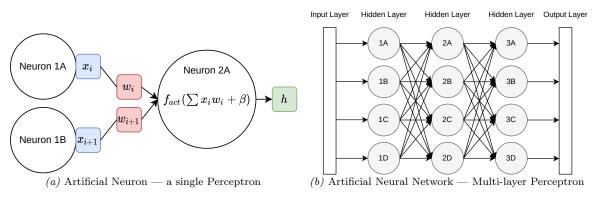

| 2.4 | A Per   | ceptron and an Artificial Neural Network           | 23 |

|     | a       | Artificial Neuron — a single Perceptron            | 23 |

|     | b       | Artificial Neural Network — Multi-layer Perceptron | 23 |

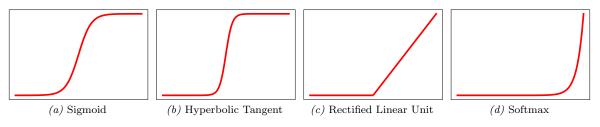

| 2.5 | Depic   | tion of popular activation functions               | 23 |

|     | a       | Sigmoid                                            | 23 |

|     | b       | Hyperbolic Tangent                                 | 23 |

|     | с       | Rectified Linear Unit                              | 23 |

|     | d       | Softmax                                            | 23 |

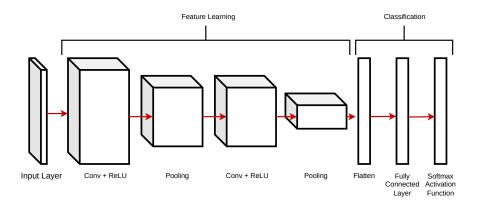

| 2.6 | Convo   | blution Neural Network                             | 28 |

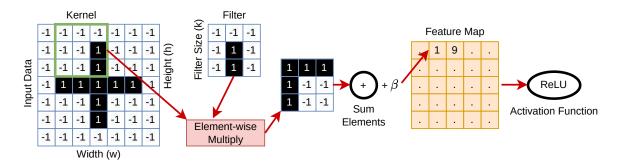

| 2.7  | Convolution operation over 2 × 2 matrix                                                            | 28  |

|------|----------------------------------------------------------------------------------------------------|-----|

|      | Convolution operation over $2 \times 2$ matrix $\ldots \ldots \ldots \ldots \ldots$                |     |

| 2.8  | Convolution over image data representing a cross                                                   | 29  |

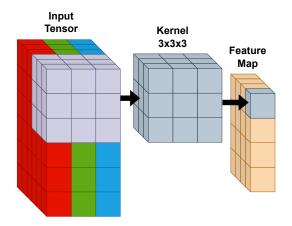

| 2.9  | Applying $3 \times 3 \times 3$ Convolution kernel to a $6 \times 6 \times 3$ input tensor          | 32  |

| 2.10 | Difference between a DNN layer and a DNN tensor operator $\ . \ . \ .$ .                           | 33  |

| 2.11 | Components and abstraction layers of DL systems                                                    | 36  |

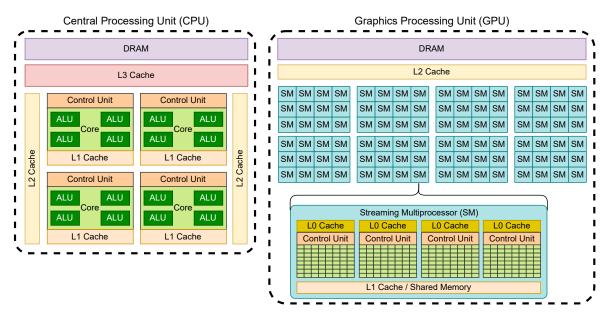

| 2.12 | Differences between CPUs and GPUs                                                                  | 39  |

| 2.13 | Evolution of a tensor operator into a tensor program                                               | 43  |

| 2.14 | Life cycle of a DL model                                                                           | 49  |

| 2.15 | Machine Learning as a Service (MLaaS) system architecture                                          | 52  |

| 2.16 | Deep Learning Compiler Design                                                                      | 63  |

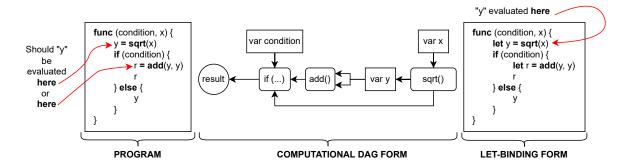

| 2.17 | Graph-based vs. Let-binding HLIR                                                                   | 69  |

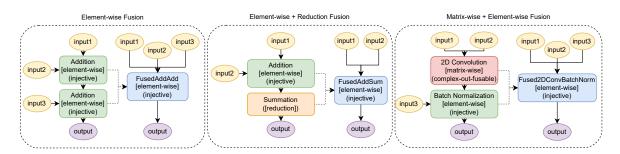

| 2.18 | Different rules of Operator Fusion                                                                 | 70  |

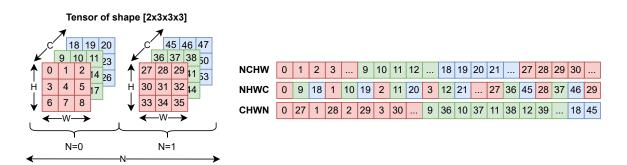

| 2.19 | Different types of tensor data layouts given the same tensor                                       | 71  |

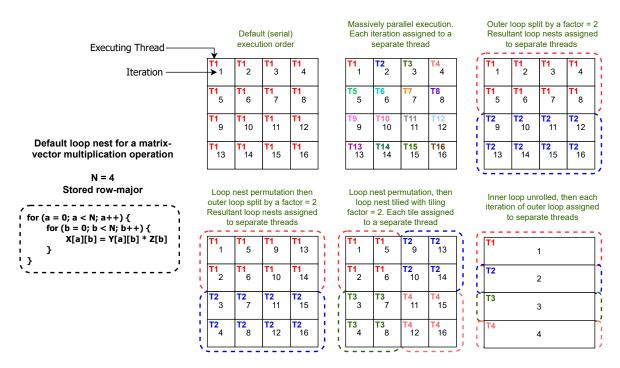

| 2.20 | Different parallelisation schemes enabled by loop nest transformations .                           | 80  |

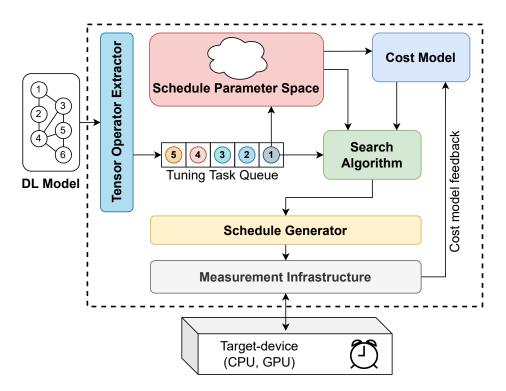

| 2.21 | Components and operation of a typical DL auto-tuner                                                | 84  |

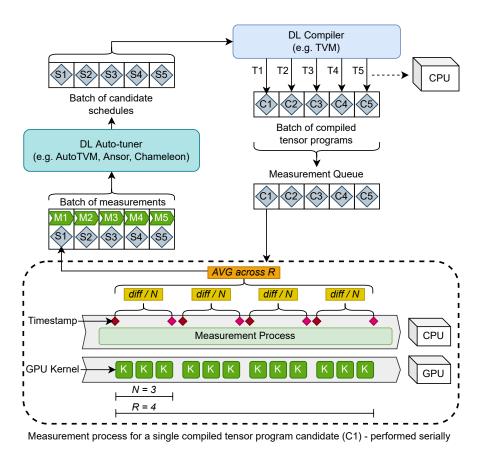

| 2.22 | DL Auto-tuner Measurement Infrastructure                                                           | 90  |

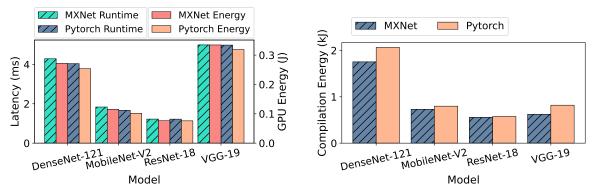

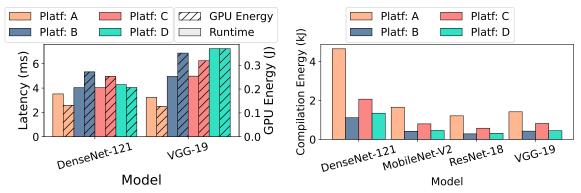

| 3.1  | Latency and energy costs, four models, two frameworks, one platform $% \mathcal{A}(\mathcal{A})$ . | 103 |

|      | a Inference latency and GPU energy cost of the converted model .                                   | 103 |

|      | b Energy costs incurred by conversion and compilation                                              | 103 |

| 3.2  | Latency and energy costs, two/four models, Pytorch, four platforms $\ . \ .$                       | 104 |

|      | a Inference latency and GPU energy cost of the converted model .                                   | 104 |

|      | b Energy costs incurred by conversion and compilation                                              | 104 |

| 3.3  | Energy costs, three models, five optimisation levels, one platform                                 | 106 |

|      | a GPU inference energy cost after optimisation                                                     | 106 |

|      | b Conversion and compilation energy costs per optimisation level .                                 | 106 |

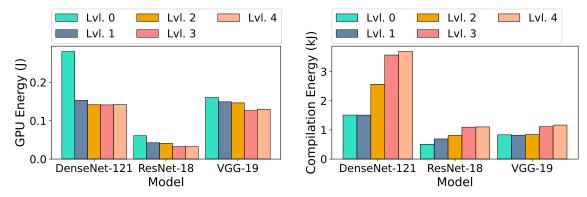

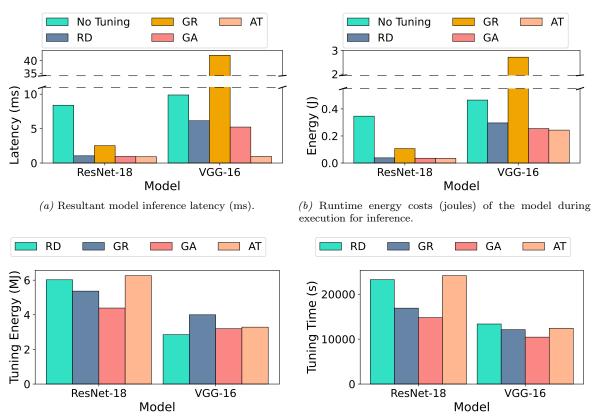

| 3.4  | Impact of auto-tuning, four auto-tuners, two models, Platform A                                    | 108 |

|      | a Resultant model inference latency                                                                | 108 |

|     | b Runtime energy costs of the model during execution for inference           | 108 |

|-----|------------------------------------------------------------------------------|-----|

|     | c Energy cost incurred from auto-tuning                                      | 108 |

|     | d Wall-clock time cost of auto-tuning                                        | 108 |

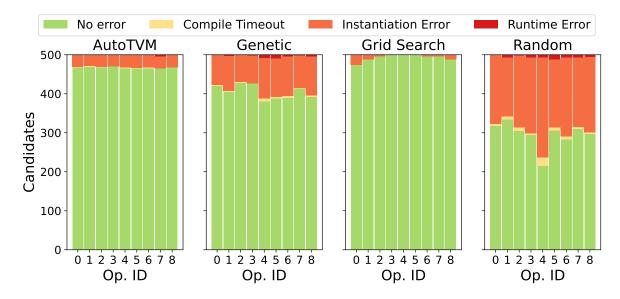

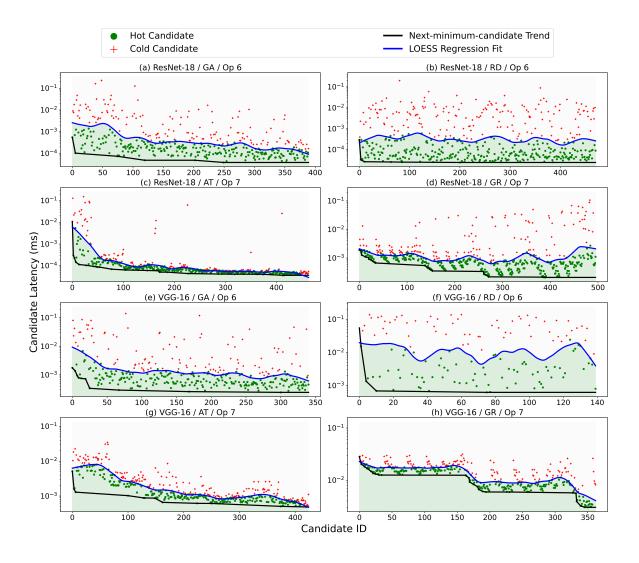

| 3.5 | Erroneous candidates, four auto-tuners, Platform A, ResNet-18                | 111 |

| 3.6 | Latency improvement trends, four auto-tuners, ResNet-18, VGG-16 $$           | 112 |

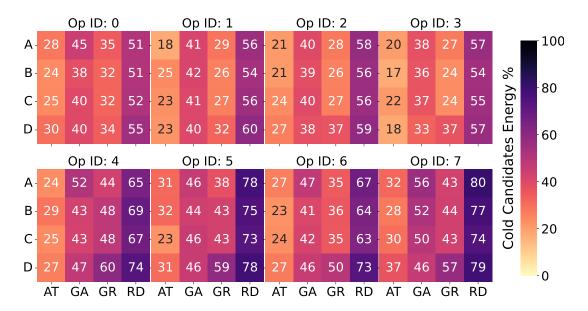

| 3.7 | Percentage of energy costs attributed to <i>cold</i> candidates              | 113 |

| 4.1 | Trimmer system architecture                                                  | 119 |

| 4.2 | Differences between Sequential and Survey tuning                             | 127 |

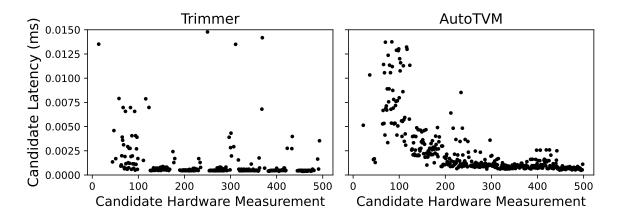

| 4.3 | Candidate latency patterns, VGG-16 OP 5, Trimmer vs. AutoTVM $$ .            | 136 |

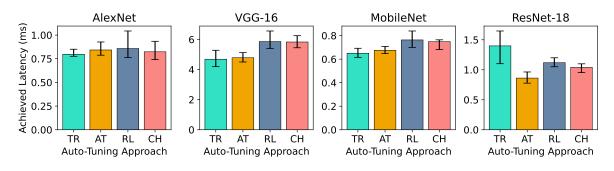

| 4.4 | Achieved inference latency (ms)                                              | 137 |

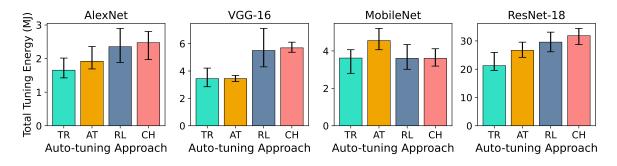

| 4.5 | Total auto-tuning energy consumption                                         | 137 |

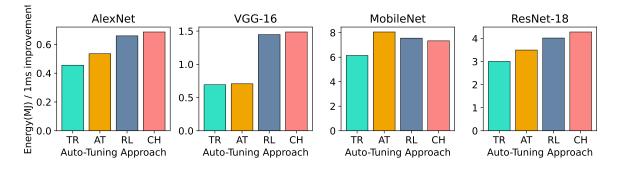

| 4.6 | Auto-tuning energy costs per one millisecond of latency reduction            | 138 |

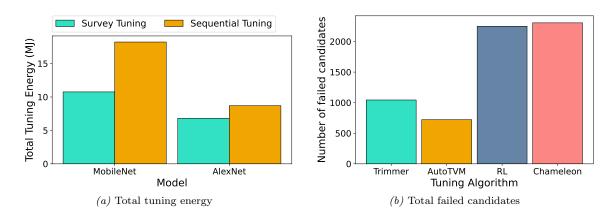

| 4.7 | Total auto-tuning energy cost & number of failed measurements $\ . \ . \ .$  | 139 |

|     | a Total tuning energy                                                        | 139 |

|     | b Total failed candidates                                                    | 139 |

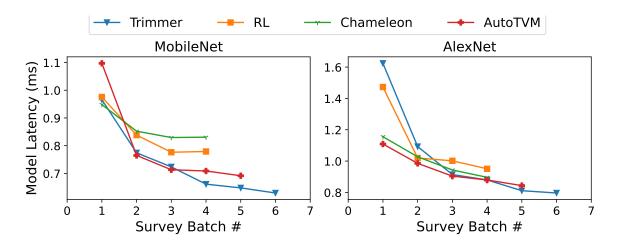

| 4.8 | DL model inference latency after Survey auto-tuning                          | 140 |

| 5.1 | Auto-tuning four DL models with three auto-tuners, Nvidia V100 $$            | 145 |

|     | a Inference latency improvement relative to default schedules                | 145 |

|     | b Auto-tuning time cost across auto-tuners and models                        | 145 |

| 5.2 | Auto-tuning three DL models with three auto-tuners, Nvidia V100              | 146 |

|     | a Auto-tuning time proportion across auto-tuning phases                      | 146 |

|     | b Average CPU and GPU utilisation during auto-tuning                         | 146 |

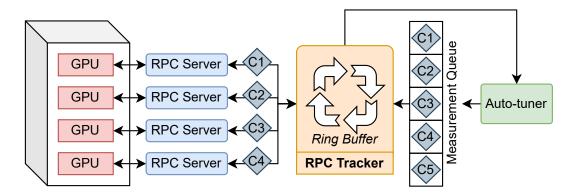

| 5.3 | Architecture of the RPC-based serial measurement infrastructure              | 149 |

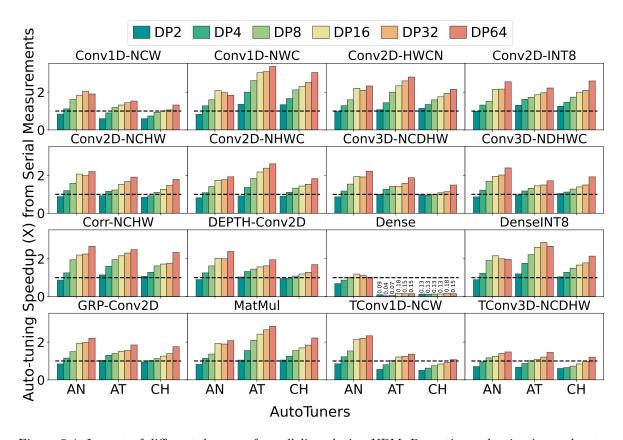

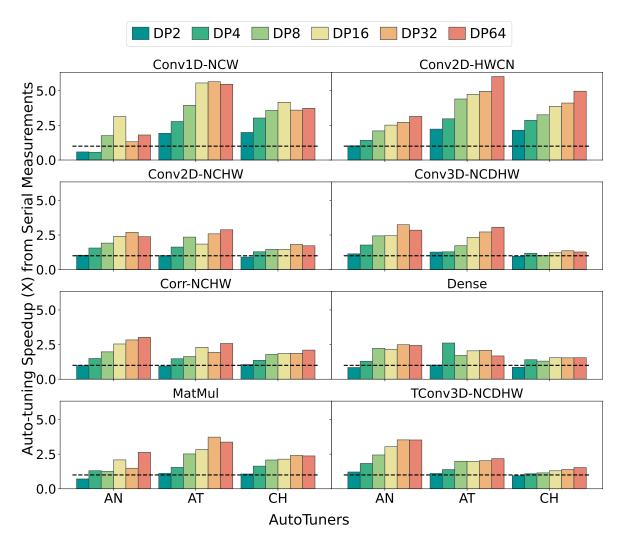

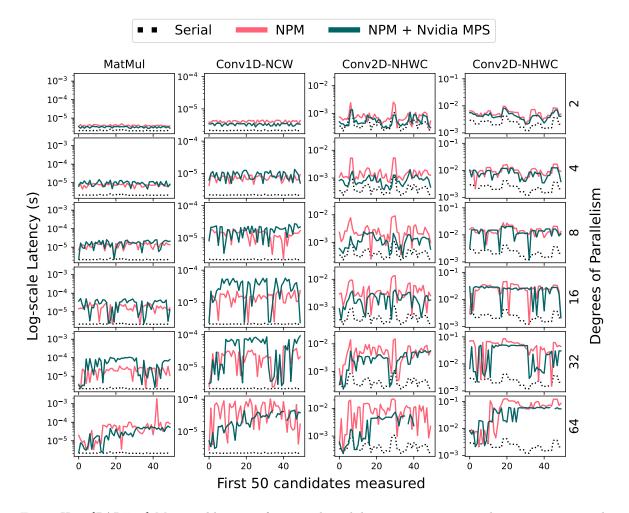

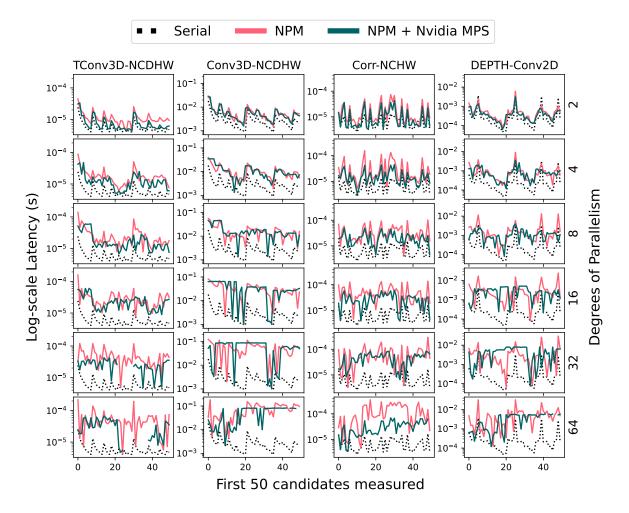

| 5.4 | Impact of different degrees of parallelism during NPM                        | 154 |

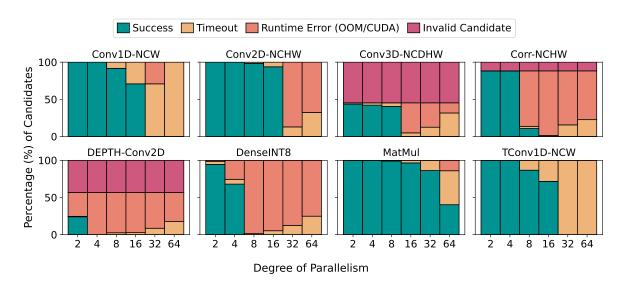

| 5.5 | Successful/failed measurements across degrees of parallelism $\ . \ . \ .$ . | 156 |

| 5.6 | Impact of the degree of parallelism during NPM with Nvidia MPS               | 158 |

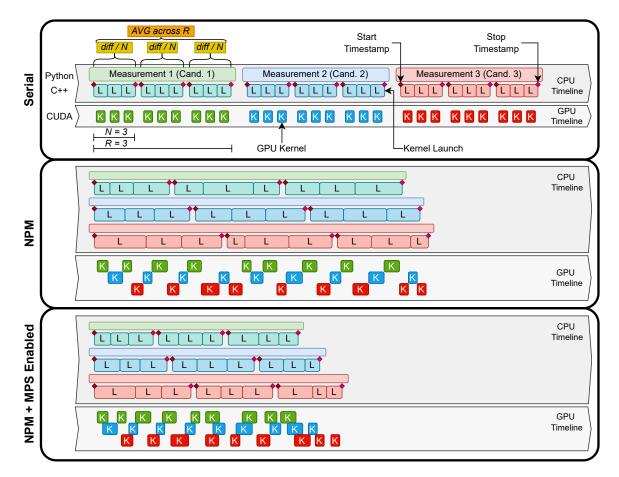

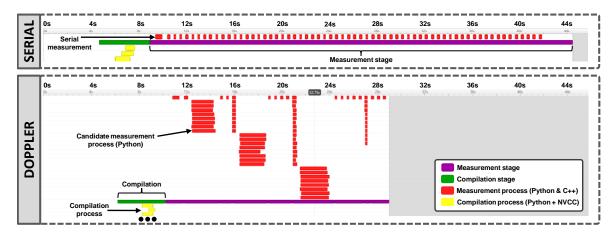

| 5.7  | Tensor program execution patterns, serial, NPM, NPM + MPS $~$                 | 159 |

|------|-------------------------------------------------------------------------------|-----|

| 5.8  | Best found tensor program across different degrees of parallelism             | 160 |

| 5.9  | Measurements across time, Grid-index, serial, NPM, NPM + MPS                  | 163 |

| 6.1  | Design of the DOPpler measurement infrastructure                              | 170 |

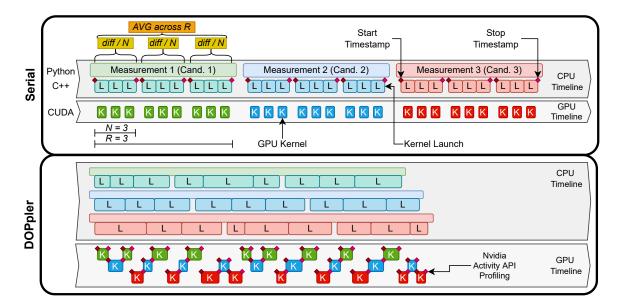

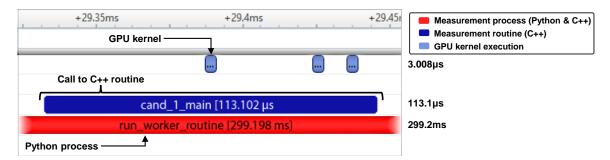

| 6.2  | Tensor program and GPU kernel execution patterns, serial vs. DOPpler          | 175 |

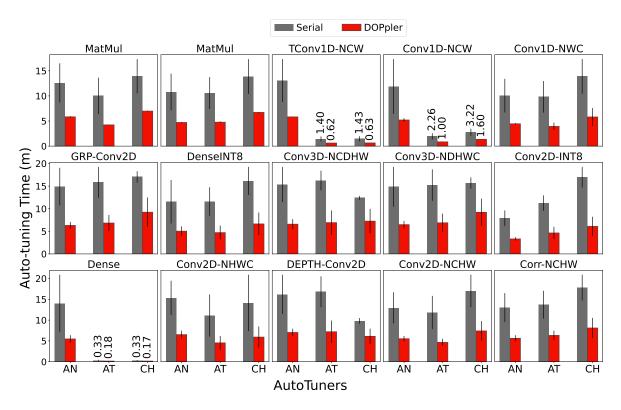

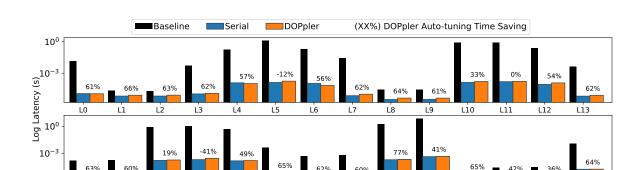

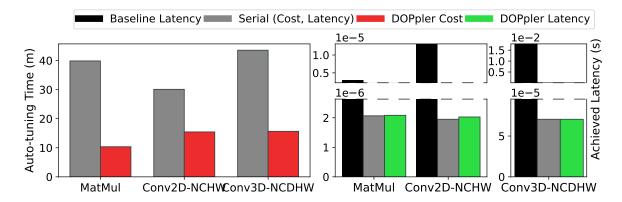

| 6.3  | Time cost, three auto-tuners, three platforms, serial vs. DOPpler $\ . \ .$ . | 188 |

| 6.4  | Achieved latency, three auto-tuners, three platforms, serial vs. DOPpler      | 189 |

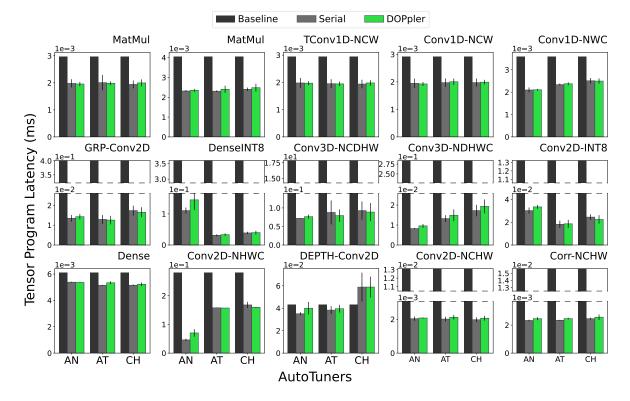

| 6.5  | Auto-tuning DL models, Ansor, serial vs. DOPpler                              | 191 |

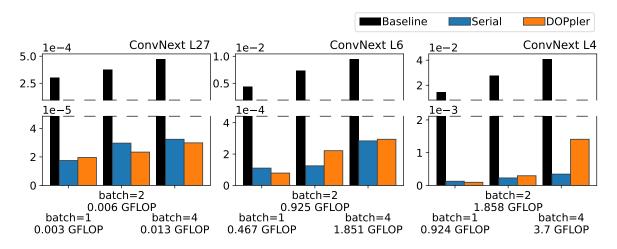

| 6.6  | Inference latency and time cost, ConvNeXt, Ansor, serial vs. DOPpler .        | 192 |

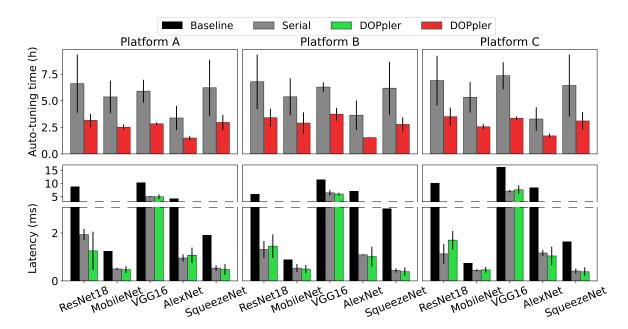

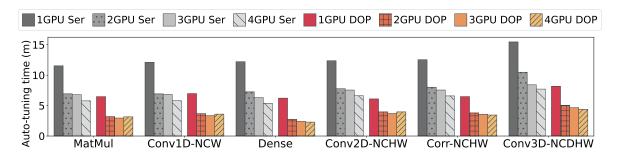

| 6.7  | Time cost, multiple target devices, serial RPC vs. DOPpler                    | 193 |

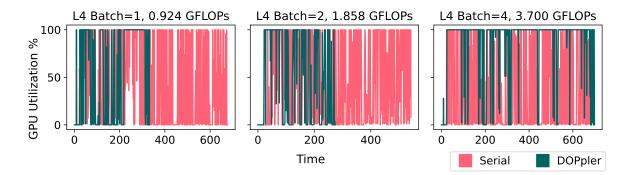

| 6.8  | GPU utilisation, Ansor, varied batch size, serial vs. DOPpler                 | 194 |

| 6.9  | Achieved latency, large layers, varied batch size, serial vs. DOPpler $$      | 194 |

| 6.10 | Latency and time cost, 2000 measurements, serial vs. DOPpler                  | 196 |

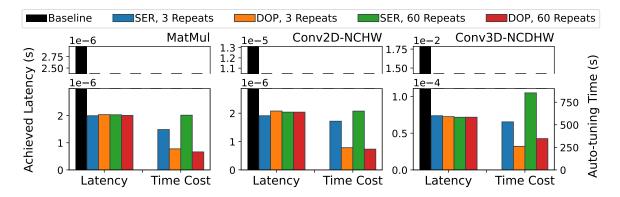

| 6.11 | Latency and time cost, varied number of repeats, serial vs. DOPpler           | 197 |

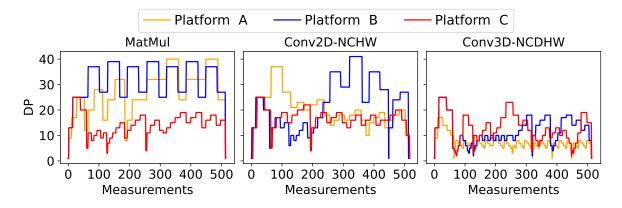

| 6.12 | Change in DOPpler's degree of parallelism across time and platforms .         | 198 |

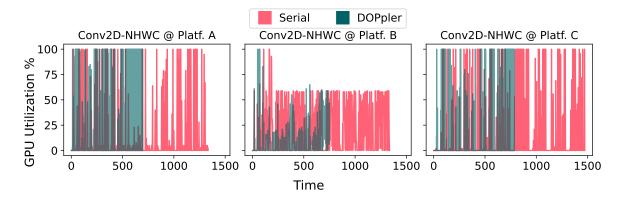

| 6.13 | GPU utilisation, multiple platforms, serial vs. DOPpler                       | 199 |

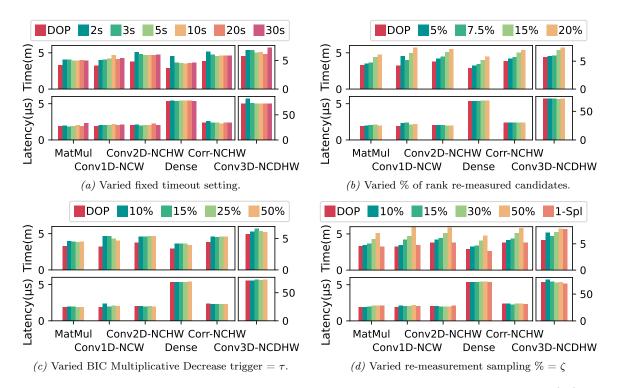

| 6.14 | DOPpler hyperparameter sensitivity study results                              | 201 |

|      | a Varied fixed timeout setting                                                | 201 |

|      | b Varied % of rank re-measured candidates                                     | 201 |

|      | c Varied BIC Multiplicative Decrease trigger = $\tau$                         | 201 |

|      | d Varied re-measurement sampling $\% = \zeta \dots \dots \dots \dots$         | 201 |

| 7.1  | Compute and cooling equipment within the server room                          | 217 |

|      | a Racks containing machines within the server room                            | 217 |

|      | b Mitsubishi Electric PKA-M100KAL CRAC                                        | 217 |

| A.1  | RNN cell depicted as a recurrent block and unrolled across time steps .       | 291 |

|      | a RNN cell                                                                    | 291 |

|      | b RNN cell across time                                                         | 291 |

|------|--------------------------------------------------------------------------------|-----|

| A.2  | LSTM gated cell                                                                | 293 |

| B.1  | Application Specific Integrated Circuit (ASIC) architecture                    | 296 |

| B.2  | Field-Programmable Gate Array (FPGA) architecture                              | 298 |

| D.2  | ried-riogrammable Gate Array (ri GA) arcmtecture                               | 298 |

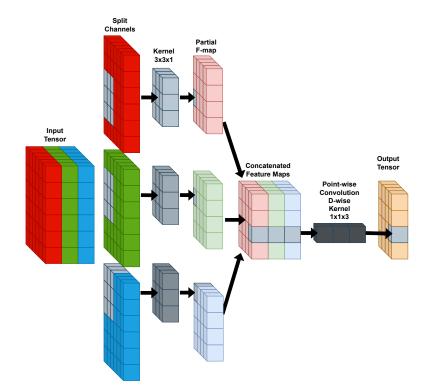

| D.1  | The effect of applying $3x3x1$ (x3) Depth-wise Separable Convolution           | 303 |

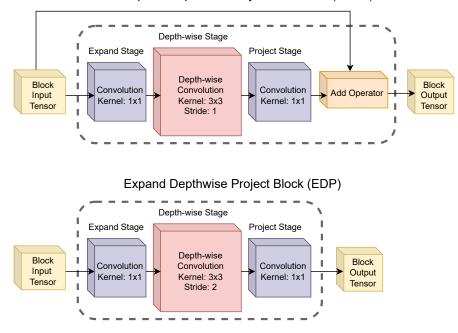

| D.2  | The Expand Depth-wise Project (Add) Blocks in MobileNetV2                      | 305 |

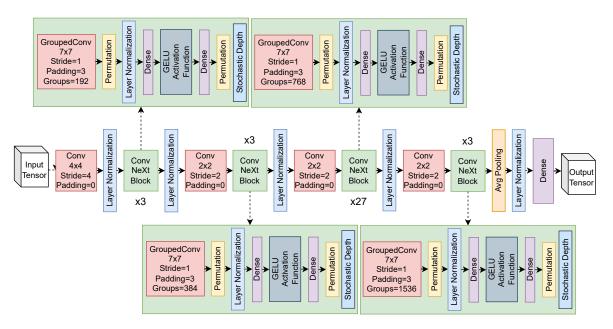

| D.3  | The ConvNeXt Blocks, Layers and overall architecture                           | 307 |

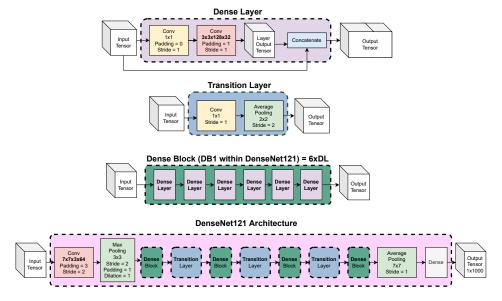

| D.4  | Dense / Transition layers, Blocks and DNN architecture of DenseNet121          | 309 |

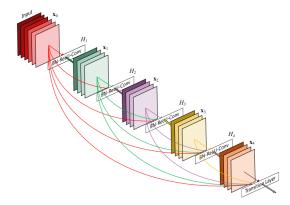

| D.5  | Connectivity between Dense layers within DenseNet121                           | 309 |

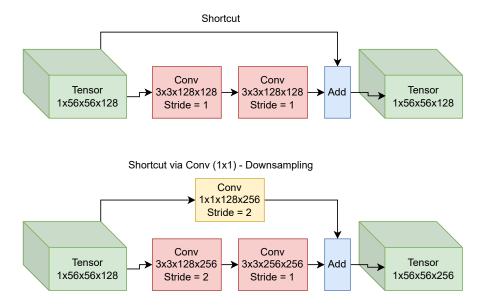

| D.6  | Depiction of the Residual Blocks in ResNet architectures                       | 311 |

| TT 1 |                                                                                | 901 |

| H.1  | {PART 1:} Latency of candidates proposed by Grid-index auto-tuner .            | 321 |

| H.2  | $\{PART 2:\}$ Latency of candidates proposed by Grid-index auto-tuner .        | 322 |

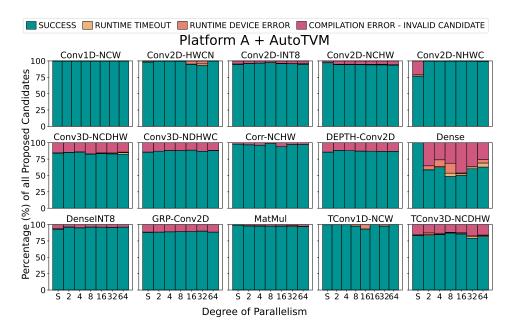

| H.3  | Measurement outcomes, 15 operator groups, AutoTVM, Platform A $$ .             | 323 |

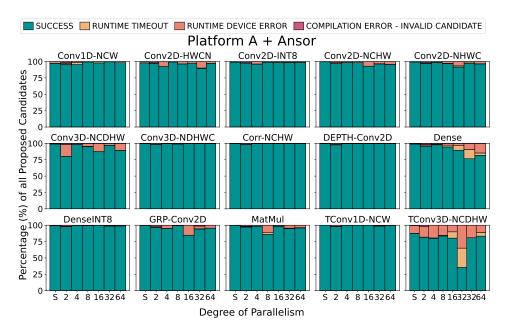

| H.4  | Measurement outcomes, 15 operator groups, Ansor, Platform A $\ \ldots$ .       | 324 |

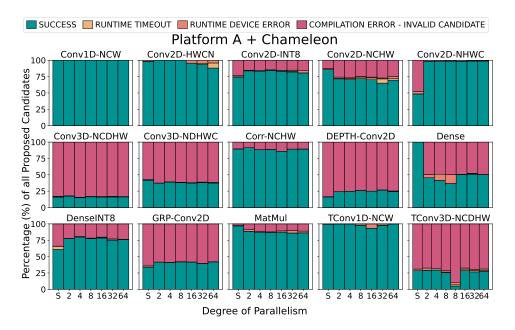

| H.5  | Measurement outcomes, 15 operator groups, Chameleon, Platform A $~$ .          | 324 |

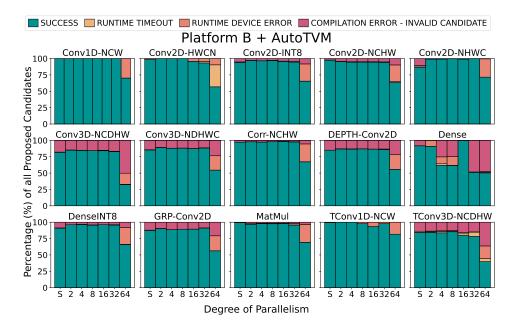

| H.6  | Measurement outcomes, 15 operator groups, AutoTVM, Platform B $$ .             | 325 |

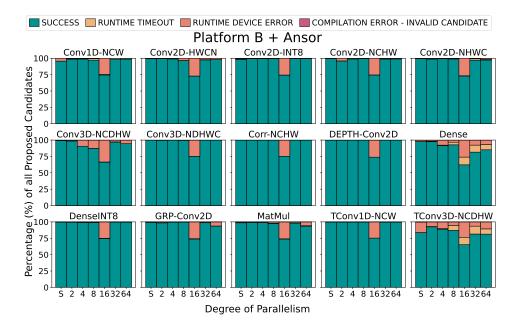

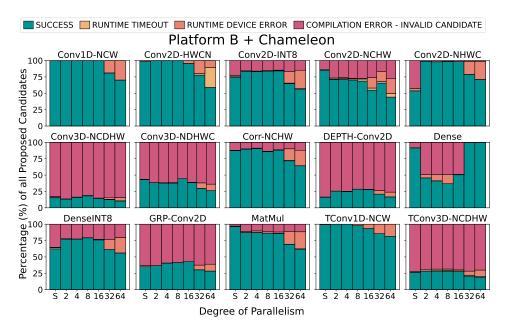

| H.7  | Measurement outcomes, 15 operator groups, Ansor, Platform B $\ .\ .\ .$        | 325 |

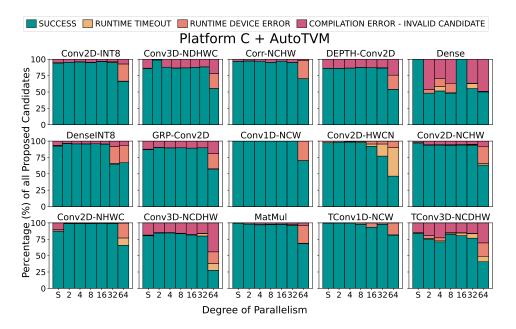

| H.8  | Measurement outcomes, 15 operator groups, Chameleon, Platform B                | 326 |

| H.9  | Measurement outcomes, 15 operator groups, AutoTVM, Platform C $_{\rm \cdot}$ . | 326 |

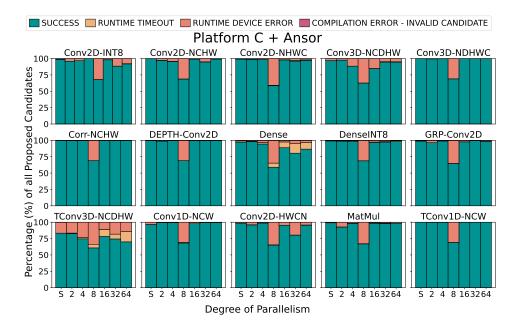

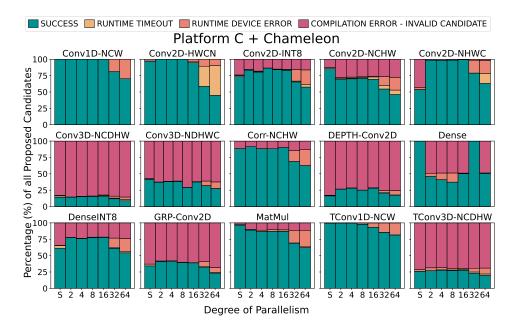

| H.10 | ) Measurement outcomes, 15 operator groups, Ansor, Platform C $\ . \ . \ .$    | 327 |

| H.11 | Measurement outcomes, 15 operator groups, Chameleon, Platform C                | 327 |

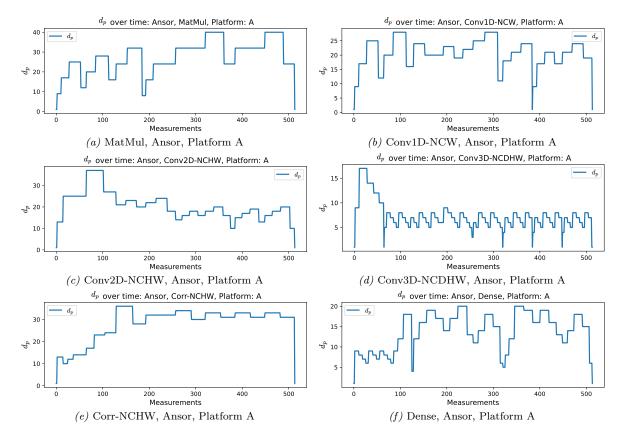

| I.1  | $d_p$ over time when auto-tuning with Ansor towards Platform A                 | 329 |

| . =  | a MatMul, Ansor, Platform A                                                    | 329 |

|      |                                                                                |     |

|      | b Conv1D-NCW, Ansor, Platform A                                                | 329 |

|      | c Conv2D-NCHW, Ansor, Platform A                                               | 329 |

|     | d          | Conv3D-NCDHW, Ansor, Platform A                                               | 329 |

|-----|------------|-------------------------------------------------------------------------------|-----|

|     | е          | Corr-NCHW, Ansor, Platform A                                                  | 329 |

|     | f          | Dense, Ansor, Platform A                                                      | 329 |

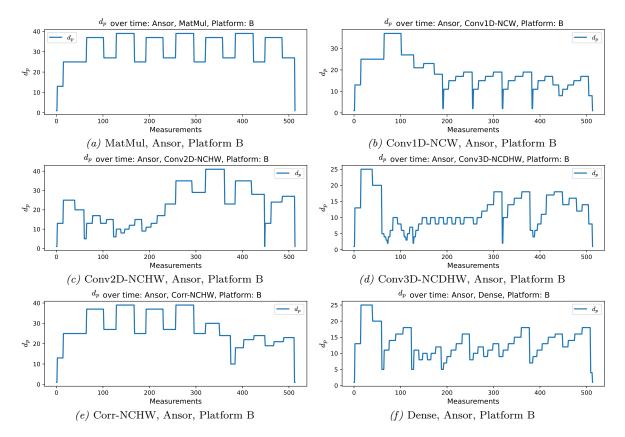

| I.2 | $d_p$ over | r time when auto-tuning with Ansor towards Platform B                         | 330 |

|     | a          | MatMul, Ansor, Platform B                                                     | 330 |

|     | b          | Conv1D-NCW, Ansor, Platform B                                                 | 330 |

|     | с          | Conv2D-NCHW, Ansor, Platform B                                                | 330 |

|     | d          | Conv3D-NCDHW, Ansor, Platform B                                               | 330 |

|     | e          | Corr-NCHW, Ansor, Platform B                                                  | 330 |

|     | f          | Dense, Ansor, Platform B                                                      | 330 |

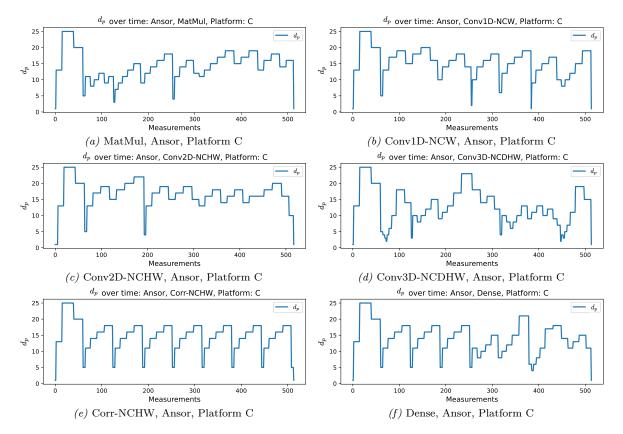

| I.3 | $d_p$ over | r time when auto-tuning with Ansor towards Platform C                         | 331 |

|     | a          | MatMul, Ansor, Platform C $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ .$           | 331 |

|     | b          | Conv1D-NCW, Ansor, Platform C                                                 | 331 |

|     | с          | Conv2D-NCHW, Ansor, Platform C                                                | 331 |

|     | d          | Conv3D-NCDHW, Ansor, Platform C                                               | 331 |

|     | е          | Corr-NCHW, Ansor, Platform C                                                  | 331 |

|     | f          | Dense, Ansor, Platform C                                                      | 331 |

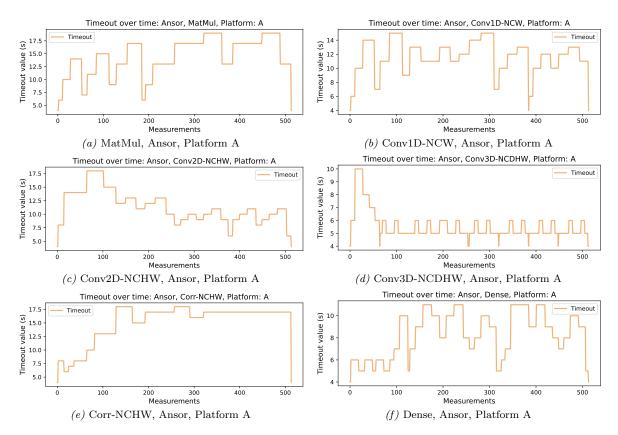

| I.4 | Timeo      | ut over time when auto-tuning with Ansor towards Platform A $$ .              | 332 |

|     | a          | MatMul, Ansor, Platform A                                                     | 332 |

|     | b          | Conv1D-NCW, Ansor, Platform A                                                 | 332 |

|     | с          | Conv2D-NCHW, Ansor, Platform A                                                | 332 |

|     | d          | Conv3D-NCDHW, Ansor, Platform A                                               | 332 |

|     | е          | Corr-NCHW, Ansor, Platform A                                                  | 332 |

|     | f          | Dense, Ansor, Platform A                                                      | 332 |

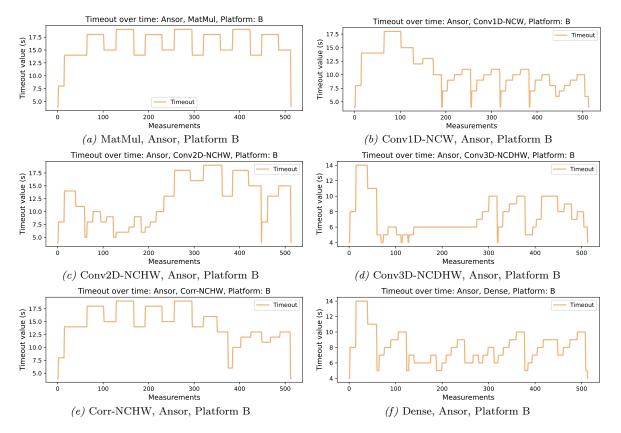

| I.5 | Timeo      | ut over time when auto-tuning with Ansor towards Platform B $% \mathcal{B}$ . | 333 |

|     | a          | MatMul, Ansor, Platform B                                                     | 333 |

|     | b          | Conv1D-NCW, Ansor, Platform B                                                 | 333 |

|     | с      | Conv2D-NCHW, Ansor, Platform B                                                      | 333 |

|-----|--------|-------------------------------------------------------------------------------------|-----|

|     | d      | Conv3D-NCDHW, Ansor, Platform B                                                     | 333 |

|     | е      | Corr-NCHW, Ansor, Platform B                                                        | 333 |

|     | f      | Dense, Ansor, Platform B                                                            | 333 |

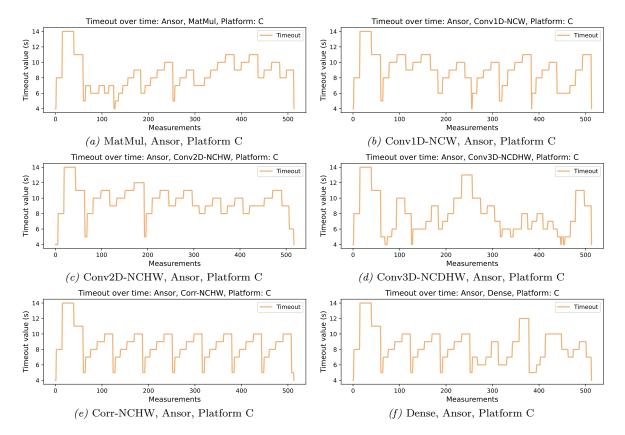

| I.6 | Timeo  | ut over time when auto-tuning with Ansor towards Platform C $% \mathcal{C}^{(n)}$ . | 334 |

|     | a      | MatMul, Ansor, Platform C                                                           | 334 |

|     | b      | Conv1D-NCW, Ansor, Platform C                                                       | 334 |

|     | с      | Conv2D-NCHW, Ansor, Platform C                                                      | 334 |

|     | d      | Conv3D-NCDHW, Ansor, Platform C                                                     | 334 |

|     | е      | Corr-NCHW, Ansor, Platform C                                                        | 334 |

|     | f      | Dense, Ansor, Platform C                                                            | 334 |

| I.7 | Proces | s-level view of auto-tuning MatMul with Serial and DOPpler                          | 335 |

| I.8 | NVTX   | $\left[238\right]$ trace at the kernel level during candidate measurement           | 335 |

This page is left intentionally blank

### List of Tables

| 2.1 | Characterisation and support matrix of popular deep learning compilers       | 64  |

|-----|------------------------------------------------------------------------------|-----|

| 2.2 | Characterisation of prominent DL compiler auto-tuners and autoschedulers     | 85  |

| 3.1 | Details of DL models used during the study                                   | 99  |

| 3.2 | Details of hardware platforms used during the study                          | 99  |

| 3.3 | Details of middleware and software used during the study                     | 100 |

| 3.4 | Cold candidate impact on time and energy costs of auto-tuning $\ . \ . \ .$  | 114 |

| 4.1 | Details of the FC network architecture used by Trimmer                       | 122 |

| 4.2 | Achieved inference latency, auto-tuning time and energy costs incurred       | 136 |

| 4.3 | Survey tuning vs. parallel model auto-tuning in a cluster scenario $\ . \ .$ | 139 |

| 5.1 | Details of hardware platforms used during experimentation                    | 150 |

| 5.2 | Details of middleware and software used during the study                     | 151 |

| 5.3 | Tensor operator workloads used during experimentation                        | 152 |

| 6.1 | Details of DL models used during DOPpler's evaluation                        | 184 |

| 6.2 | Time cost and latency improvement, three auto-tuners, three platforms        | 187 |

| 7.1 | Experimentation time, energy and environmental cost estimates $\ldots$       | 221 |

| 7.2 | Environmental and financial experimentation cost estimates across locations  | 222 |

| 7.3 | Estimated costs of performing experimentation in the Cloud                   | 222 |

| C.1 | Tensor Operator Characteristics                                                                                                 | 300 |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-----|

| D.1 | AlexNet [168] architecture details                                                                                              | 301 |

| D.2 | SqueezeNet [130] architecture details                                                                                           | 302 |

| D.3 | MobileNetV1 [121] architecture details                                                                                          | 304 |

| D.4 | MobileNetV2 [288] architecture details                                                                                          | 306 |

| D.5 | ConvNeXt [194] architecture details                                                                                             | 308 |

| D.6 | DenseNet121 [125] architecture details                                                                                          | 310 |

| D.7 | ResNet-18 [113] architecture details                                                                                            | 312 |

| D.8 | VGG-16 [304] architecture details                                                                                               | 313 |

| D.9 | VGG-19 [304] architecture details                                                                                               | 314 |

| E.1 | TVM's Relay IR transformation passes                                                                                            | 315 |

| F.1 | Schedule parameters used to parameterise templates during auto-tuning.                                                          | 316 |

| F.2 | Grid-index auto-tuner configuration details                                                                                     | 316 |

| F.3 | Random auto-tuner configuration details                                                                                         | 316 |

| F.4 | Genetic auto-tuner configuration details                                                                                        | 317 |

| F.5 | AutoTVM auto-tuner configuration details                                                                                        | 317 |

| F.6 | Chameleon auto-tuner configuration details                                                                                      | 317 |

| F.7 | Ansor auto-tuner configuration details                                                                                          | 318 |

| I.1 | Kernel and tensor program execution timings, Nvidia NVTX / N<br>sight $% \mathcal{N} = \mathcal{N} = \mathcal{N} + \mathcal{N}$ | 336 |

## List of Listings

| 2.1 | Naïve, deep loop nest implementation of Convolution        | 45  |

|-----|------------------------------------------------------------|-----|

| 2.2 | Simple matrix multiply implementation in CUDA              | 47  |

| 2.3 | GEMM loop nest example                                     | 73  |

| 2.4 | Loop permutation example                                   | 77  |

| 2.5 | Loop fusion example                                        | 77  |

| 2.6 | Loop unrolling example                                     | 77  |

| 2.7 | Loop splitting example                                     | 77  |

| 2.8 | Loop tiling example                                        | 78  |

| 2.9 | Vectorisation example                                      | 81  |

| G.1 | Pytorch implementation of Trimmer's FC ANN filtering model | 319 |

List of Listings

### List of Abbreviations

- AaaS Auto-tuning as a Service

- **ALU** Arithmetic Logic Unit

- **AMX** Advanced Matrix Extensions

- **ANN** Artificial Neural Network

- **API** Application Programming Interface

- **ASIC** Application Specific Integrated Circuit

- AT AutoTVM

- AVX Advanced Vector Extensions

- **BIC** Binary Increase Congestion control

- **BN** Batch Normalisation

- **CHP** Combined Heat and Power

- **CI** Computational Intensity

- **CLB** Configurable Logic Block

- ${\bf CNN}\,$  Convolution Neural Network

- **CPU** Central Processing Unit

- **CRAC** Computer Room Air Conditioning

CUDA Compute Unified Device Architecture

**CUPTI** CUDA Profiling Tools Interface

${\bf CV}\,$  Computer Vision

DAG Directed Acyclic Graph

**DDR** Double Data Rate

**DL** Deep Learning

**DNN** Deep Neural Network

**DRAM** Dynamic Random Access Memory

**DSL** Domain Specific Language

**DSP** Digital Signal Processor

**EDP** Expand-Depth-wise-Project

EDPA Expand-Depth-wise-Project-Add

$\mathbf{FC}$  Fully-connected

${\bf FFNN}$  Feed-forward Neural Network

${\bf FFT}$  Fast Fourier Transform

**FLOP** Floating-point Operation

FMA Fused Multiply-Add

FMAC Fused Multiply-Accumulate

FP Floating-point

FPGA Field-Programmable Gate Array

**FPU** Floating-Point Unit

**GA** Genetic Algorithm

**GAN** Generative Adversarial Networks

${\bf GBT}\,$  Gradient Boosted Trees

**GDDR** Graphics Double Data Rate

**GEMM** General Matrix Multiply

GFLOPs Giga Floating-point Operations

${\bf GHG}\,$  Greenhouse Gas

**GOPS** Giga Operations

GPU Graphics Processing Unit

${\bf GR}~{\rm Grid}~{\rm Index}$

**HBM** High Bandwidth Memory

HDO Hardware-Dependent Optimisations

HLIR High-Level Intermediate Representation

**HWCN** (H)eight - (W)idth - (C)hannels - Batch-size(N)

**IC** Image Classification

${\bf IE}~$  Inference Engine

**INT** Integer

**IPC** Instructions per Cycle

IPU Image/Intelligence Processing Unit

**IR** Intermediate Representation

**ISA** Instruction Set Architecture

**LLIR** Low-Level Intermediate Representation

LLVM Low-Level Virtual Machine

LSTM Long-short Term Memory

${\bf LUT}$ Lookup Table

MAC Multiply Accumulate

MAD Multiply Add

MIG Multi Instance GPU

ML Machine Learning

**MLaaS** Machine Learning as a Service

**MPS** Multi-process Service

MSR Model-Specific Register

**NAS** Neural Architecture Search

NCHW Batch-size(N) - (C)hannels - (H)eight - (W)idth

NHWC Batch-size(N) - (H)eight - (W)idth - (C)hannels

- **NLP** Natural Language Processing

- ${\bf NNP}\,$  Neural Network Processor

- ${\bf NPM}\,$ Naïve Parallel Measurement

- NPU Neural Processing Unit

- **NVML** Nvidia Management Library

- **ONNX** Open Neural Network Exchange

- **OOM** Out-of-memory

- $\mathbf{OPS}$  Operations

- **PE** Processing Element

- **PPM** Precise Parallel Measurer

- **PPO** Proximal Policy Optimisation

- **PSU** Power Supply Unit

- **RAPL** Running Average Power Limit

- ${\bf RD}\,$  Random Index

- ${\bf ReLU}$  Rectified Linear Unit

- ${\bf RF}\,$  Random Forest

- **RL** Reinforcement Learning

- ${\bf RNN}\,$  Recurrent Neural Network

**RPC** Remote Procedure Call

- **SA** Simulated Annealing

- **SDP** Spatial (Dataflow) Processor

- SIMD Single-Instruction Multiple-Data

- **SIMT** Single-Instruction Multiple-Threads

- $\mathbf{SM}$  Simultaneous Multiprocessor

- **SMT** Simultaneous Multi-threading

- SOTA state-of-the-art

- TC TensorComprehensions

- TCP Transmission Control Protocol

- **TDP** Thermal Design Power

- **TE** Tensor Expression

- ${\bf TFLOPs}\,$  Tera Floating-point Operations

- **TIP** Temporal (Instruction) Processor

- **TOPI** Tensor Operator Inventory

- **TOPS** Tera Operations

- **TPU** Tensor Processing Unit

- ${\bf TVM}\,$  Tensor Virtual Machine

- ${\bf VPU}\,$  Vision Processing Unit

# Chapter 1

# Introduction

# 1.1 Motivation

In the recent years, Deep Learning (DL) - an area of computer science, focused on solving pattern and feature extraction tasks such as image recognition, text generation or game-playing via the use of Deep Neural Networks (DNNs), has significantly impacted many industries such as autonomous transport, social media, finance or scientific applications, achieving impressive predictive performance [129, 205, 380, 95, 169]. With the proliferation of DL models, there is an ever-increasing demand for them to be accurate, generic and fast at performing inference, reflected by the growing access to on-demand compute infrastructures supporting DL workloads [131, 295, 55, 99]. Such success is in part enabled by developments in DL systems - ecosystems of software and hardware that support high-level DL model prototyping, training and deployment for inference. DL systems utilise computational capabilities of high-performance Central Processing Units (CPUs) and compute accelerators such as Graphics Processing Units (GPUs) to execute model training and inference [275].

Developing and operating high performance DL models and systems that support them, requires significant engineering effort, computational power and financial investment [33, 303, 258, 204, 308]. Furthermore, the most generally applicable<sup>1</sup> and accurate models also tend to exhibit the highest operational costs due to their algorithmic complexity, need for prolonged training and large computational footprint during inference [332, 152]. However, operational costs are commonly a second-order concern in modern DL systems research and industrial developments, focusing foremost on improving model designs for increased accuracy and generality, whilst designing novel DL accelerator architectures such as GPUs, Tensor Processing Units (TPUs), Neural Processing Units (NPUs), and DL-specific Application Specific Integrated Circuits (ASICs) to perform more computation more quickly [67, 275, 324].

## 1.1.1 High Operational Costs in Deep Learning

While the algorithmic complexity of DL models is the primary cause for majority of the operational costs in DL deployments [65], inefficient utilisation of the compute resources (for example, GPUs) that underpin DL systems can vastly inflate these costs [368, 144, 123, 146]. DL engineers commonly design and train DL models using highlevel DL frameworks such as Pytorch [1] or TensorFlow [2], whilst their deployment on high-performance hardware is facilitated using DL inference engines [327, 85, 240], internally supported by acceleration libraries [51, 232, 141]. At each of these levels of the software stack, great care is taken to provide efficient implementations for common DL model tensor operators<sup>2</sup>, however, these efforts often fail to keep up with the development of novel DL model architectures (and their unique tensor operators), and continual developments in the area of high-performance, massively-parallel processors that underpin DL computation [39, 105]. This forces DL frameworks and inference engines to use sub-optimal tensor operator implementations for compatibility reasons, which leads to resource under-utilisation and inflated operational costs [39, 176, 173].

<sup>&</sup>lt;sup>1</sup>Capable of performing multiple learning tasks such as image classification with object detection.

<sup>&</sup>lt;sup>2</sup>Tensor operators are primary components within DL models that specify the mathematical operations to be performed as part of training and inference.

## 1.1.2 Optimising Model Inference Performance

A traditional approach to improve execution latency, compute resource utilisation and thus cost-efficiency of performing DL computation on high-performance hardware, is for the DL engineer to manually develop optimal *tensor programs* that implement individual tensor operators within a given DL model. With the current diversity of quickly changing operational DL environments, manually ensuring that each new DL model tensor operator is implemented optimally towards each of the progressively more powerful *target-devices* is infeasible, given the complexity of DL system deployments. Such manual optimisation of DL tensor operators must take into account a range of unique DL model architectures, multiple DL frameworks that can facilitate DL model development, tens to hundreds of unique tensor operators per DL model, a range of unique target-devices that can be leveraged to perform tensor computations of the DL models, and potentially billions of unique implementations (tensor program candidates) of a single tensor operator towards a single target-device.

## **1.1.3** Deep Learning Compilers

As a result, various DL compilers [39, 262, 18, 173, 307, 382] have gained prominence by enabling automated transformations of high-level DL model computation specifications (originating from DL frameworks), into sets of executable tensor programs (implementations of tensor operators) that execute on a variety of targetdevices, including high-performance GPU accelerators. Effectively, DL compilers enable automated decoupling of the computation specification (for example, highlevel mathematical descriptions) from the way in which such computations should be performed on target-devices (for example, loop nest structures, memory data layouts, thread parallelism). Furthermore, DL compilers facilitate DL model graph-level transformations that optimise the overall model architecture towards faster inference. DL compilers relieve some of the engineering burden associated with developing high-performance DL model implementations, however, they require DL engineers to provide *schedules* - sets of program transformations that describe how a given DL tensor operator should leverage computational resources of a high-performance targetdevice. For example, within the TVM [39] DL compiler, such schedules take form of a configurable template of a tensor program, which accepts parameters that determine how the high-level tensor operator expression will map to low-level tensor program operations during compilation, including thread-level parallelism, data access, operation synchronisation and loop nest transformations. As such, while some of the complexity of implementing DL models is relieved by DL compilers, the process of determining schedule parameters that configure tensor programs remains manual<sup>3</sup> during the use of standalone DL compilers. As previously outlined, there can be in the order of billions of unique *candidate* schedules for any combination of a tensor operator and a target-device, that must be evaluated on the target-device to determine their performance.

### 1.1.4 Deep Learning Compiler Auto-tuning

In an attempt to further alleviate the engineering burden of discovering high-performance tensor program schedules, the concept of DL *auto-tuning* has been proposed [40]. Facilitated by DL compilers, DL auto-tuning automates discovery of optimised schedules via the use of cost models and search algorithms that help to traverse the enormous *schedule space*, followed by on target-device execution latency measurements of promising tensor program candidates, ultimately resulting in a schedule configuration proposal for a given tensor operator and target-device combination that results in reduced inference latency of the end-to-end DL model. Many DL auto-tuners have recently been proposed [40, 8, 385, 183, 377, 386, 105, 373], each utilising a different set of component variants

$<sup>^3\</sup>mathrm{The}$  DL engineers must test different schedule parameters for combinations of tensor operator classes and target-devices

(for example, cost models, search strategies or schedule spaces), improving efficacy of DL optimisation by targeting increasingly more diverse ranges of tensor operator classes and target-devices, resulting in substantial DL model inference speedup [40, 385]. One component that nearly all state-of-the-art (SOTA) DL auto-tuners share in common is the measurement infrastructure, which manages candidate tensor program execution latency measurements. It is important to note that all such measurements are performed in isolation - that is one at a time, ensuring accuracy of measurement and reliability of the infrastructure, which when coupled with extensive schedule space exploration leads to prolonged auto-tuning time [8, 183, 385].

## 1.1.5 Costs of Optimising Deep Learning Model Inference

Through the use of high-level DL model graph optimisations and DL auto-tuners, both facilitated by DL compilers, DL engineers can substantially reduce end-to-end DL model inference latency when executing DL models on a given target-device [39, 18, 345, 388, 8, 385, 183]. However, the specific relationships between optimisation quality and time and energy costs of performing them, have not been previously explored nor quantified.

This is especially the case for DL auto-tuning. The process of optimisation via DL auto-tuning can be observably time and energy-expensive (taking several days in the case of large models [184]), yet the precise reasons why that is have not been studied. While auto-tuning times in the range of tens of hours per end-to-end DL model may be acceptable in sporadic, one-off usage patterns, prolonged auto-tuning of individual models at a Cloud cluster level, or when models have to be re-tuned towards different execution scenarios, begins to become a challenging problem. This is further amplified by the isolation of the target-device during DL auto-tuning, reducing device availability and increasing operational costs. As such, to start introducing any modifications to the existing DL auto-tuning infrastructures, it is necessary to first analyse and quantify the phenomena responsible for cost-inefficient DL auto-tuning.

# 1.2 Recent Challenges within DL Auto-tuning

DL auto-tuners exhibit several outstanding research challenges towards achieving costefficient DL inference performance optimisation.

### **1.2.1** Serial Candidate Latency Measurements

All SOTA DL auto-tuners utilise a similar approach to performing on-target-device latency measurements of candidate tensor programs [40, 385, 8]. This approach involves isolating the target-device and performing candidate tensor program latency measurements serially, in sequence, ensuring only a single kernel executes at the targetdevice at a time. This stems from a long-standing, held and practised assumption within the DL auto-tuning community that introducing any degree of parallelism will inevitably result in interference due to resource contention and unpredictability of GPU kernel scheduling. While unequivocally ensuring measurement reliability, such an approach significantly under-utilises the available compute resources, whilst reserving them for prolonged periods of time. Addressing this bottleneck could improve both the overall wall-clock auto-tuning time and the candidate measurement throughput, resulting in improved cost-efficiency of performing DL optimisations.

## 1.2.2 Sequential End-to-end Auto-tuning

SOTA DL auto-tuners that claim to support end-to-end DL model auto-tuning [40, 39, 8, 183], rely upon sequential optimisation of tensor operators. More specifically, given an end-to-end DL model architecture definition, DL auto-tuners decompose the architecture graph into individual tensor operators and optimise each of them from start to finish, subsequently moving onto the next queued tensor operator to be optimised.

Given the current design of DL auto-tuners, achieved (optimised) end-to-end DL model inference latency can only be measured once all of its individual tensor operators have been optimised. This prevents the model-level optimisation strategy from leveraging information about end-to-end inference latency of the model when performing optimisation of its individual tensor operators, for example, to avoid unnecessary autotuning whenever this would be appropriate and cost-efficient. There is a large potential in leveraging such intermediary information, however, existing DL auto-tuners do not provide these capabilities to their users.

# 1.2.3 Unfiltered Candidate Measurements

During DL auto-tuning, cost models and search algorithms traverse the schedule space to discover configurations exhibiting low-latency for each DL model tensor operator. Subsequently, batches of such candidate schedules are proposed for on-target-device measurements in isolation to ascertain their quality and guide the schedule search. Auto-tuners combine such online measurements with optimisation strategies such as Simulated Annealing [342] that provide eventual guarantees of optimal schedule discovery after a large number of evaluations, which can be time consuming.